My FPGA PCIe客户案例70:带FMC接口(LPC)的黑金K7开发板(Kintex7-325T-FFG900)

1、准备好开发环境和硬件设备

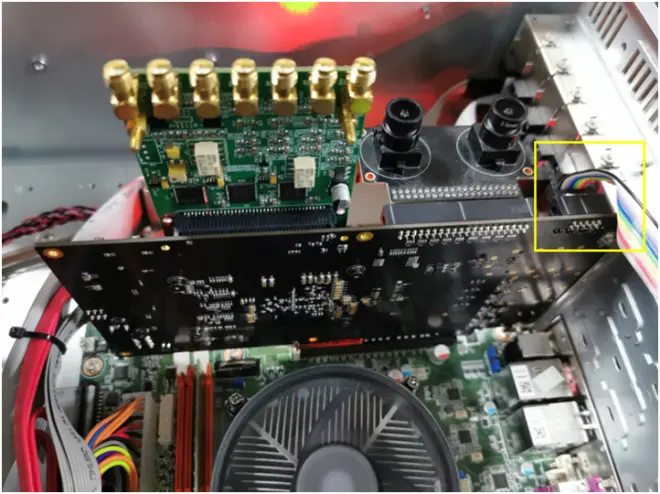

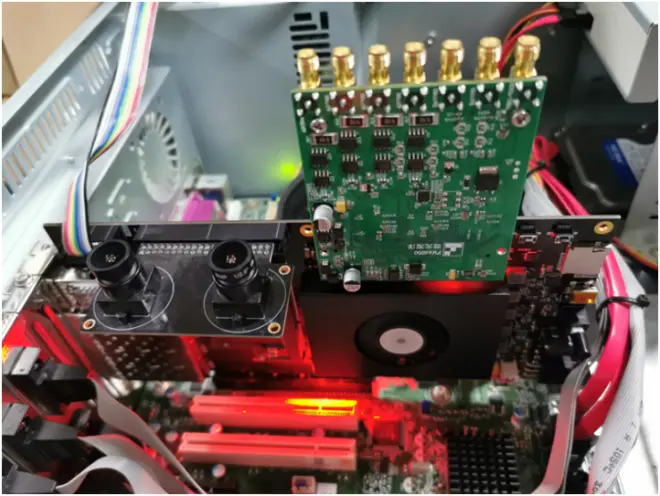

1)本节实验用来验证PCIe通信的是黑金出品的高性能Kintex7 PCIe开发板(代号:AX7325),上面板载了一颗325T-FGG900 FPGA芯片,实物如图70-1~70-4所示。

2)将黑金Kintex7 FPGA开发板插到工控机机箱里面,如图70-5所示,注意,机箱不要上电,不能带电插!

2、下位机FPGA程序开发

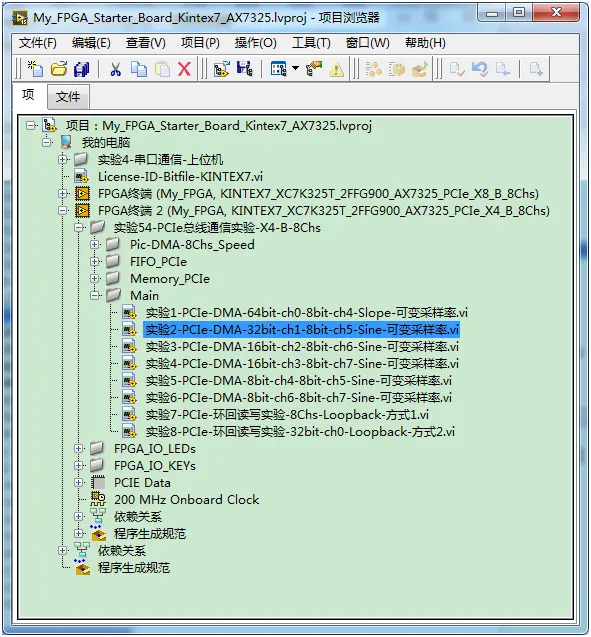

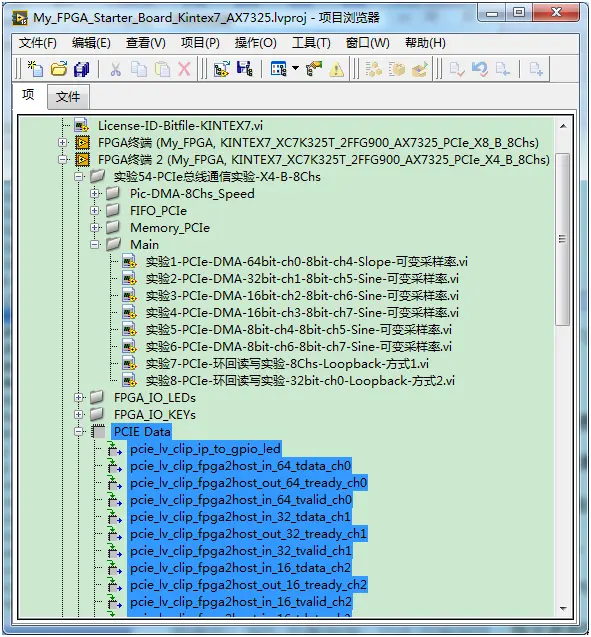

1)打开LabVIEW,新建一个带PCIe的FPGA终端(Kintex-7-325T-FGG900),编写下位机FPGA高速PCIe DMA 数采程序和上位机PC端采集控制显示程序,完整的项目如图70-6所示。封装到LabVIEW里面的K7 PCIe DMA CLIP,如图70-7所示。方便用户直接调用PCIe节点进行通信。

2)具体的下位机FPGA程序和上位机PC端的程序编写过程,这里就不再介绍了,用户可以直接参考我们给出的例程,相信只要用户把本书前面的LabVIEW FPGA PCIe基础实验和中级实验学会了,这里实战的时候也是信手拈来。

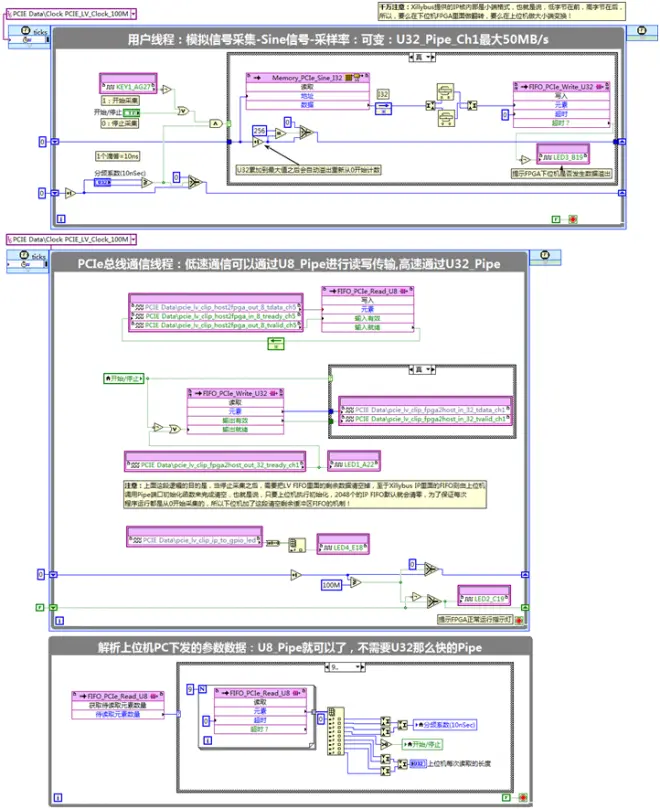

图70-8显示的是下位机FPGA上的程序框图。一共3个线程搞定:模拟ADC采集线程、PCIe传输线程、指令参数解析线程。

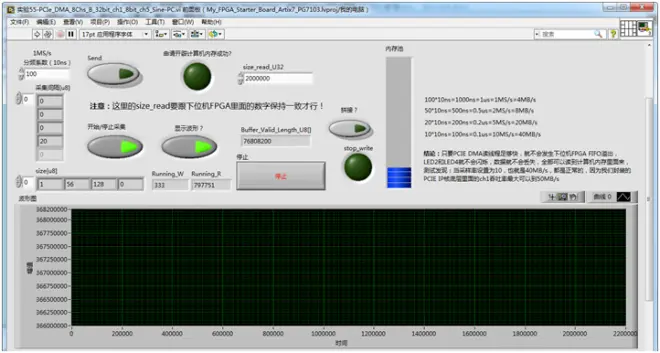

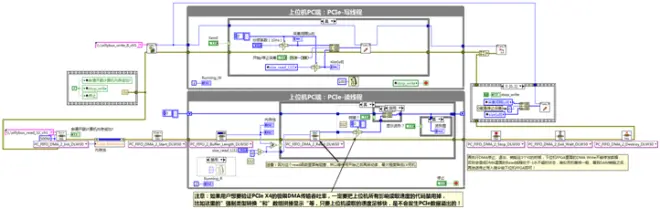

图70-9显示的是上位机PC端的数据采集前面板,图70-10显示的是上位机程序框图。上位机比较简单,直接参考前面中级实验里面的改改适配一下就可以了!

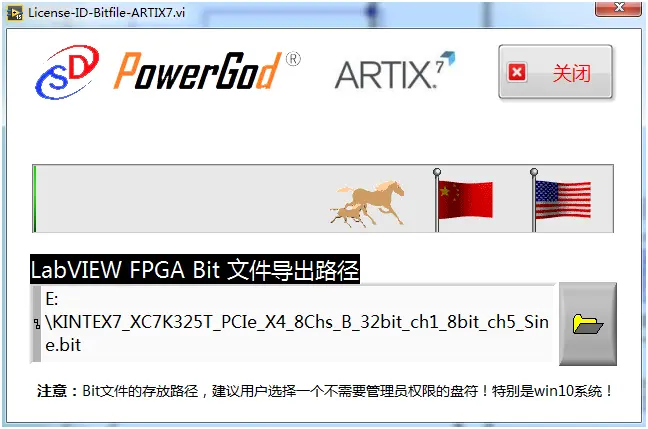

3)FPGA程序编写完成后,打开获取Kintex7 FPGA bit文件的软件,如图70-11所示。

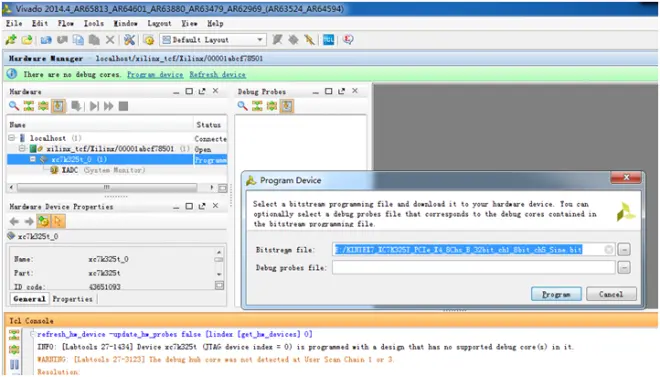

4)接下来,将工控机上电,将Xilinx下载器接到电脑上,将前面编译出来的bit文件(KINTEX7_XC7K325T_PCIe_X4_8Chs_B_32bit_ch1_8bit_ch5_Sine.bit)通过Vivado软件下载到K7开发板里面运行,下载过程如图70-12所示。

3、实验测试结果

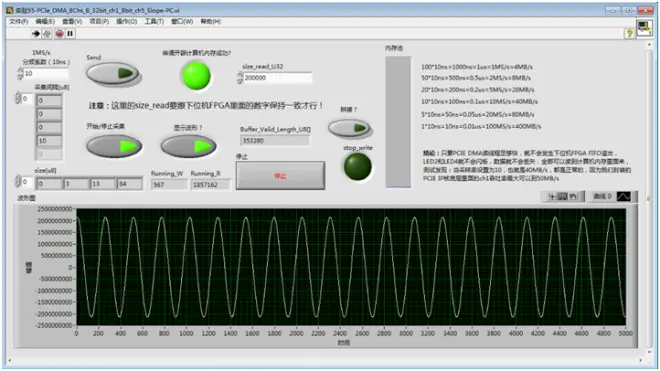

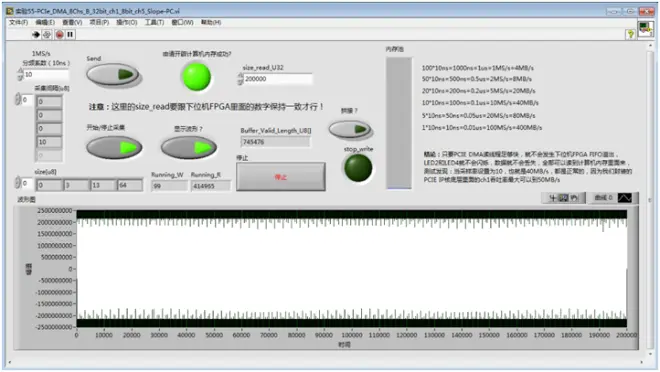

1)PCIe不支持热插拔,所以FPGA程序下载之后,需要右击热启动一下电脑,不能选择关机,必须是重启电脑,这样主板不会掉电。重启之后,运行上位机测试软件,将PCIe通道1的采样率设置为10MS/s,实际传输带宽是40MB/s(I32),采集到的原始波形,如图70-13所示。注意:由于默认的PCIe Xillybus IP里面我们将Ch1的带宽设置的是50MB/s,实际上自动分配模式下,往往达不到这个带宽,所以当用户提高采样率的时候,FPGA开发板上的LED2和LED4会出现闪烁,说明PCIe传输过程中丢点了,关于这个说明我们在前面的中级实验里面跟大家讲过了!两种解决方式:一是将Ch1通道带宽人为设置大一些,并强制分配资源;二是将数据量大的利用串转并变成U64之后,通过Ch0发送出去。

2)上面的波形数据点数太多,看不到细节,为此,我们可以利用放大镜观察一下里面的波形细节,比如显示5000个,如图70-14所示。可以看出,采集到的波形还是挺漂亮的!