FPGA实现UART(RS232)串口通信

参考:正点原子ZYNQ,野火升腾FPGA

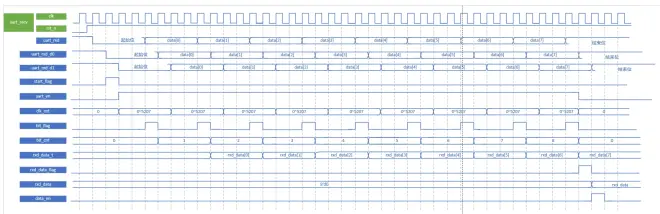

UART_RX接收端

uart_rx作为接收端,输入信号uart_xd先延迟两个时钟同步到系统时钟clk域中,组合逻辑检测uart_tx的下降沿作为数据接受起始信号。设置本次传输波特率为9600bps,则对于50MHZ的时钟而言,每个波特率周期计数次数为50M/9600=5208次。每当计数器记到5208次中间时,此时数据相对稳定便于提取当前传输的数据,把bit_flag提取一位数据标志信号拉高,bit_cnt计数一次。通过case语句,当bit_flag拉高时,把对应的数据寄存到rxd_data_t临时寄存器内,最后uart_en传输有效信号拉低时把rxd_data_t赋值给rxd_data并发出去。

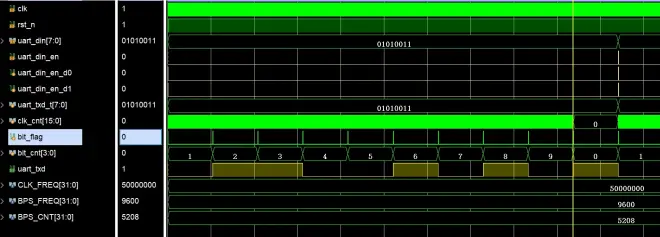

UART_TX发送端

TX端输入有uart_din数据接口和uart_data_en数据有效接口,当检测到uart_data_en为高电平时,把uart_din输入数据寄存。计数器开始计数(0~5207),每当计数器为1时,bit_flag拉高,且bit_cnt累加。通过case语句,当bit_flag拉高,根据此时bit_cnt给uart_txd赋值,从而把数据发送出去。

UART(RS232)环回

uart_rx和uart_tx与电脑串口助手连接

FPGA按键控制发送字符数据给电脑

通过按键按下开始把char_send模块里写入的字符数据传给uart_tx模块发送给电脑串口助手

按下按键,FPGA自动发送字符数据给电脑串口(按键模块没写好,触发了两次)