IEEE 1149.10介绍

背景介绍

IEEE 1149.1标准的全称是IEEE Standard for Test Access Port and Boundary-Scan Architecture。从名字中可以看出,起初1149.1是为了边界扫描(Boundary-Scan)测试而提出的,实现这一目标的电路结构是测试访问端口(TAP)。随着测试技术的发展,最新版1149.1标准将自身功能界定为以下三部分:

测试芯片之间的互连(PCB板上);

测试芯片本身;

在芯片正常工作期间观察或修改电路活动。

而本文所要介绍的1149.10的全称是IEEE Standard for High-Speed Test Access Port and On-Chip Distribution Architecture。那么两者有何不同呢?

从1149.1到1149.10

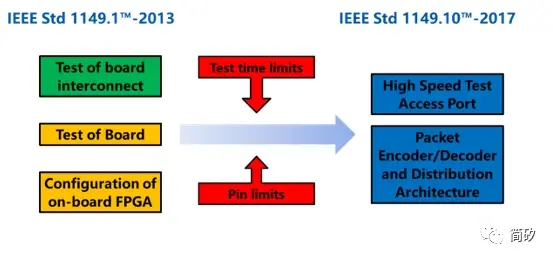

测试时间一直以来都是片上系统(system on a chip, SoC)的一个重要指标。使用原有的IEEE 1149.1测试访问端口(TAP)足以完成简单的电路板互连测试,但随着需要通过TAP进行的片上操作的增加,继续使用IEEE 1149.1 TAP进行电路板测试和配置电路板上的FPGA(现场可编程逻辑门阵列,field programmable gate array)的效率变得很低。对于大型FPGA来说,这一配置过程往往需要数十分钟。显然,IEEE 1149.1 TAP对于量产SoC测试来说实在是太慢了。

另一个问题是引脚的限制。对于小型封装(package)或裸片(die),IEEE 1149.1 TAP在测试时需要的大量引脚并不总是能够满足。

那么1149.10是怎么做的呢?

【一个例子】

我们想在一个芯片上实现10 Gbit/s的数据传输速率,而每个接触点(touch-down)的速率仅仅只有100 Mbit/s,那发送数据、接收数据就分别需要100个接触点,从而组成100条满足100 MHz时钟速率的扫描链。此外,我们还需要TAP的TCK、TMS、TDI、TDO端口。这就是1149.1的方式。

IEEE标准1149.10-2017™提供的替代方案是,使用一个差分接收器和一个差分发射器构成的高速IO接口(例如PCIe)提供相同的测试数据带宽,也就是仅需要四个数据收发引脚和一个系统时钟。

IEEE 1149.10架构

IEEE 1149.10标准包含哪些内容呢?

一个用于传送测试数据的高速测试访问端口(high speed test access port, HSTAP);

一个用于描述测试有效载荷(test payload)的数据包(packet)格式;

一个用于转换芯片上测试结构的测试数据的分配架构。(packet encoder/decoder and distribution architecture, PEDDA)

下图展示了HSTAP的daisy-chain连接方式,每个HSTAP都通过相应的PEDDA访问待测设备。

HSTAP电路是PEDDA的主要接口,它的作用是向PEDDA提供数据。

PADDA的作用是访问片上扫描通道,其结构包括一个HSTAP接口,一个扫描通道接口和一个可选的IEEE 1149.1 TAP接口。

在ATE机台与HSTAP之间,数据以Packet的方式传输。1149.10中packet的一般格式为:

包起始控制符 (Start-of-Packet, SOP);

命令字节(Command, CMD);

命令专用数据(PAYLOAD);

32-bit循环冗余校验(CRC32);

4个包终止(End-of-Packet , EOP)控制符。

IEEE 1149.10应用

IEEE 1149.10标准引入了复用任务模式引脚的思想,通过使用HSTAP和PEDDA实现高带宽测试(high-bandwidth test),如3D chiplets的die间测试数据传输,或者服务于LPCT(Low Pin Count interface)等引脚资源有限的测试场景(low resource based test)。除此之外,1149.10提供了更短的测试和配置时间,放宽了对ATE引脚的要求,还有可能降低扫描时钟速率和压缩系数。IEEE 1149.10标准代表着芯片测试技术的未来,我们可以拭目以待。