栅压自举开关设计与仿真(bootstrap,tsmc28nm工艺)

采样率fs=5GHz,T=75°C,差分输入输出,单端输入范围0.25~0.75V,最大谐波为HD3,目标值是HD3<-65dB。

采用tsmc28nm工艺,在ss工艺角下仿真,所有管子取最小长度L=30n。电源电压VDD=0.9V。

fft取256个点,仿真频率取质数7,61, 27,在保持周期的中央取点。

tran仿真未开噪声,时钟周期是200ps,仿真maxStep选20ps。

采用理想时钟,时钟周期200ps(CLK),上升/下降时间10ps,无反相延时。

1. 单管开关电阻

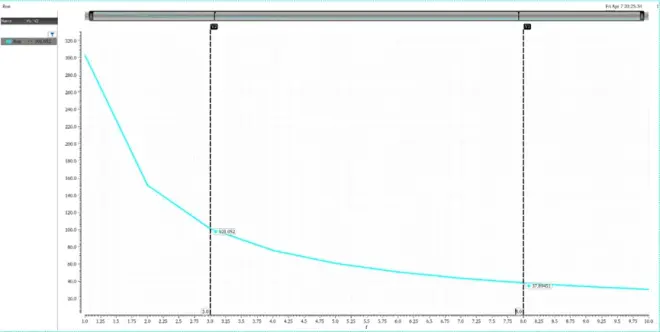

可将电阻电容结构看成一个RC低通滤波器,传递函数H(S)=,允许其引入的误差为0.5dB,则有Ron=44.5Ω。

当L=30n,W=8u时,Ron=37.89Ω(Vin=0.75V)

2. 单管采样

在ADC中,当信号输入幅度最大(A=0.5),信号频率(fin=2.5G)最高时,输出信号谐波失真最大。

信噪比表达式为,2表示差分结构。假设量化噪声很小,kT/C噪声引起信号的衰减为1dB,即。

当△=1mV,T=75°=348K,玻尔兹曼常数k=1.38*10-23。带入可得C1=445fF≈500fF。

MOS管的开关导通电阻Ron和C1构成了低通滤波器,其传递函数的模值为,经过这个RC网络之后我们不妨假设信号已经衰减了0.5dB,则有,其中频率为2.5GHz,可得Ron=44.5Ω。

可知当L=30n,W=8u时,Ron=38.13Ω。下面进行仿真可得:

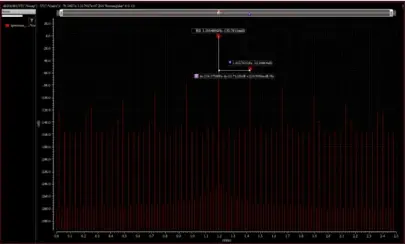

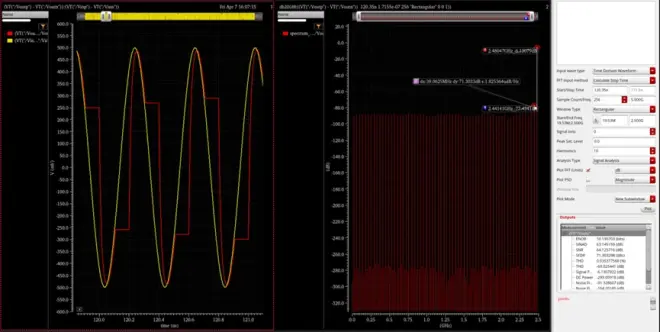

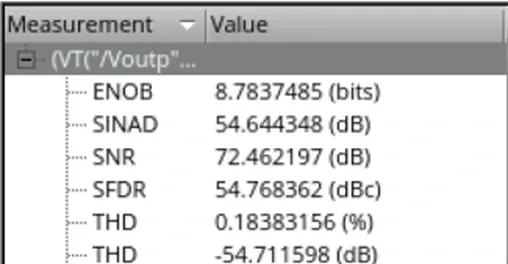

SINAD=87.40dB,THD=-87.40dB,HD3=-87.45dB(f=136.7M,M=7)

SINAD=52.67dB,THD=-52.67dB,HD3=-52.84dB(f=1.19G,M=61)

SINAD=42.58dB,THD=-42.58dB,HD3=-42.61dB(f=2.47G,M=127)

这也是符合输入信号频率越高,引起的失真越大,即HD3越大。这是由于体效应的影响,只有增大W来减小Ron来提升非线性,一直增大到24u才满足要求,结果如下:

SINAD=113.10dB,THD=-113.10dB,HD3=-113.20dB(f=136.7M,M=7)

SINAD=77.49dB,THD=-77.50dB,HD3=-77.50dB(f=1.19G,M=61)

SINAD=65.14dB,THD=-65.14dB,HD3=-65.20dB(f=1.19G,M=127)

3. ideal sample and hold

结果如下:

在fin=2.47G时,SINAD=63.15dB,THD=-69.03dB,HD3=-71.33dB(f=1.19G,M=127),达到了设计指标。

4. real sample and hold

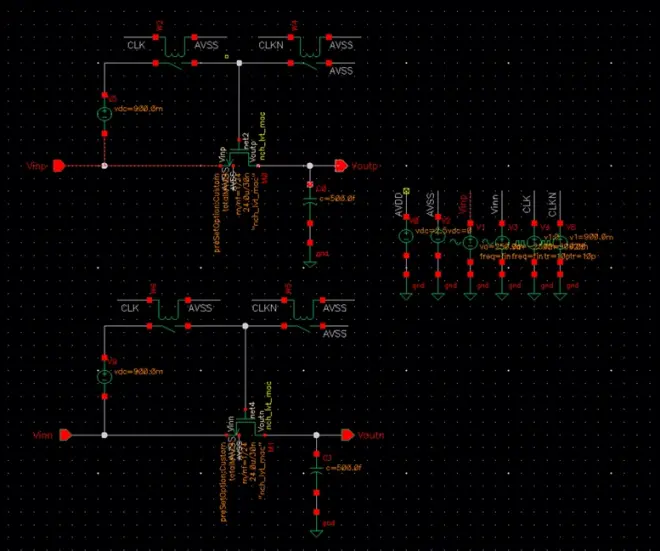

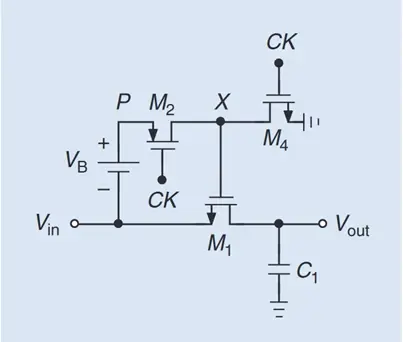

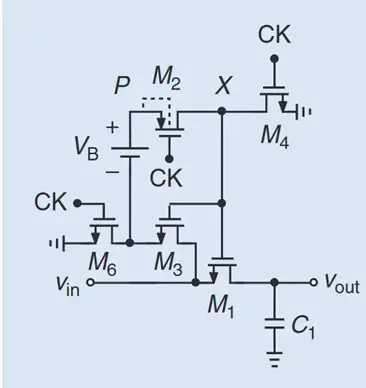

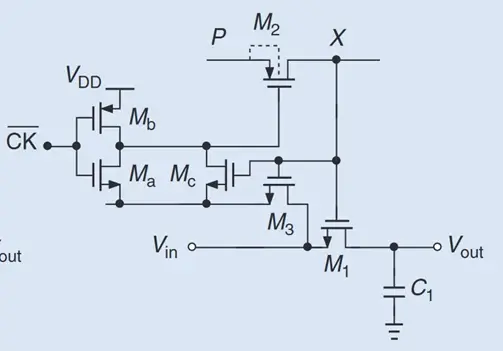

注意为了防止PMOS管衬底PN结发生击穿,应当将其Bulk端接到P端,M2和X节点处的电容形成了一个低通滤波器,会使输入信号到达X出产生失真,且M2和M4的导通电阻决定了X点电压上升的快慢。

因此我们估计CX=30fF,令,即,解得Ron=212Ω,结合前面的仿真可知W=3u,Ron=101Ω(留些余量)

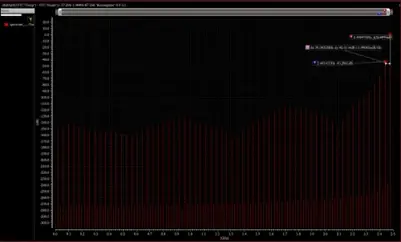

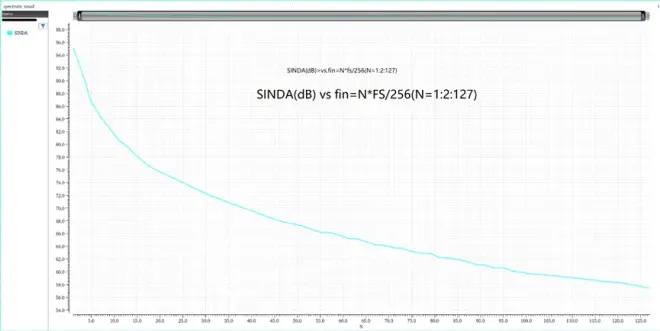

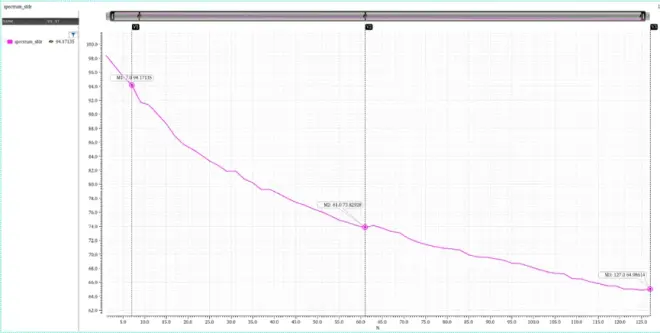

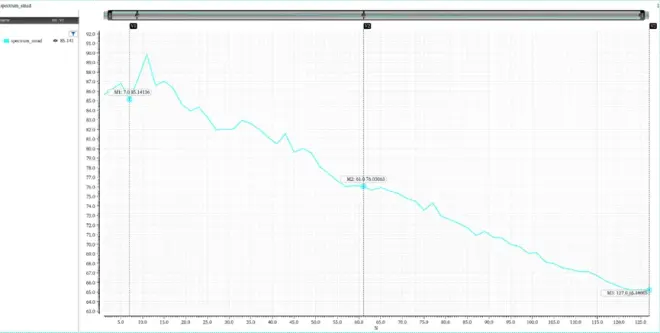

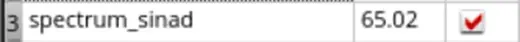

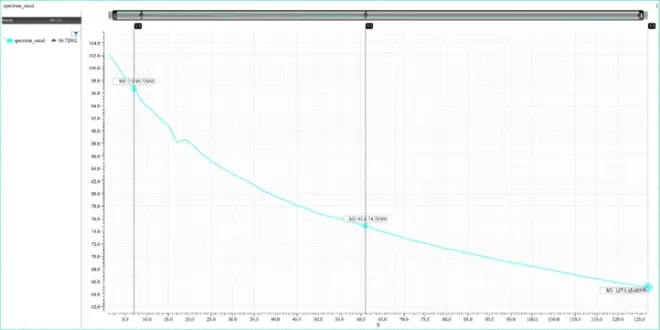

SINDA与输入频率fin之间的关系如下所示,可以发现接近奈奎斯特频率时,性能出现较大损失。

性能出现较大损失的原因是M2无法彻底关闭,使得X节点不能被M4拉倒地,下面提出改进型。

解决问题的关键是将M2与输入端断开,如下所示。

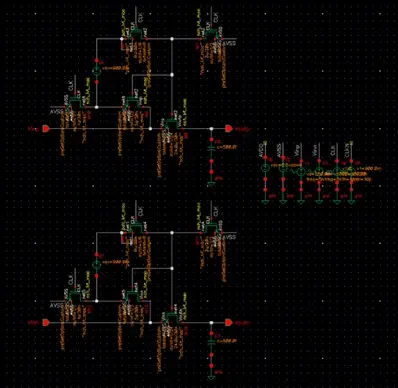

M3的导通电阻英语M2相同,故选择其W=3u,至于M6对速度的影响不是很大,令其W=1u,但值得注意的是X节点的寄生电容也同时增大了,输入信号回路的时间常数几乎增大了一倍,故将M2的W提升至6u。

仿真结果如下所示:

可以看出在输入信号接近奈奎斯特频率时,性能刚刚达到设计目标。

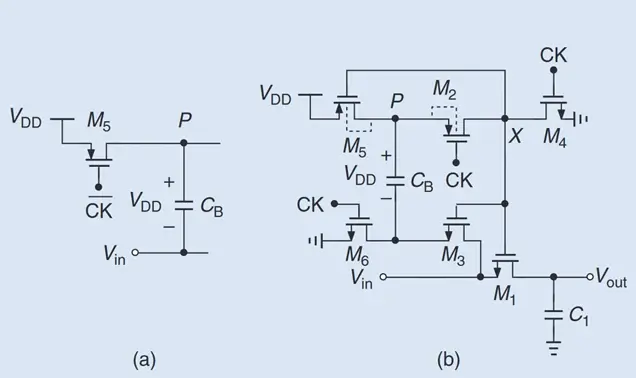

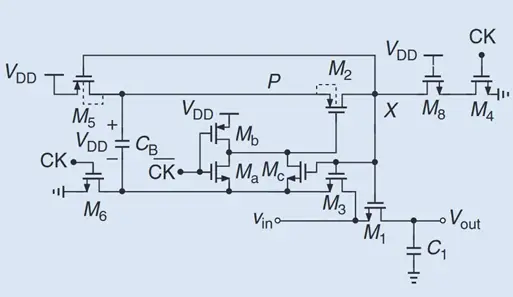

5. 将VB换成实际电容

换成电容后,同样需要一个PMOS管M5将其一段充电至VDD,至于M5的栅极控制信号,因为P的电压VP最大可能到达1V+0.75V=1.75V,若M5栅极结CLK信号则M5无法在采样状态关断,造成新能损失,故同样将其栅极连接到X点即自举到VDD+Vin。M5的n-well也到接到P点,防止正向PN结导通。

为了减少在采样状态CB和X节点寄生电容的电荷分享效应对P的电压的影响,CB要尽可能大,我们首先选择CB=500fF试试看。M5和M6的大小决定了CB充电速度的快慢。他们与CB构成的时间常数必须小于时钟周期的一半。TCK/2=100ps,CB=500pf,则要求M5和M6的导通电阻小于200Ω。结合之前的仿真结果,选择其W=2u。

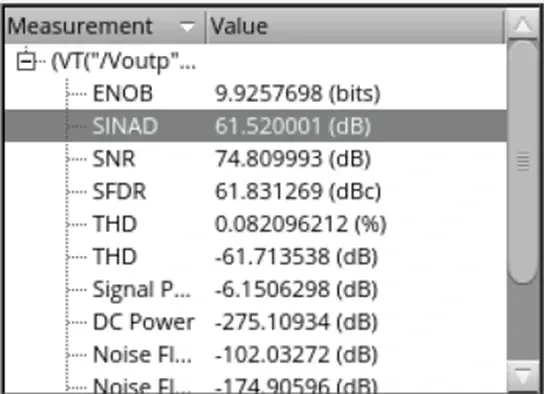

在fin=2.47G下仿真结果如下所示。

可以看出HD3=61.83Ω,猜测是M5和M6的回路的时间常数还是不达到要求,增大其W至3u。

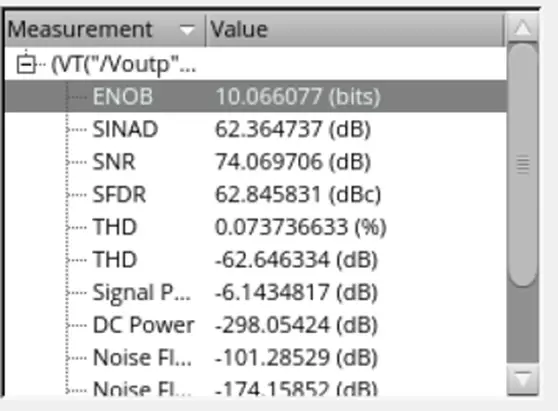

M5和M6的W至3u,仿真结果如下所示。

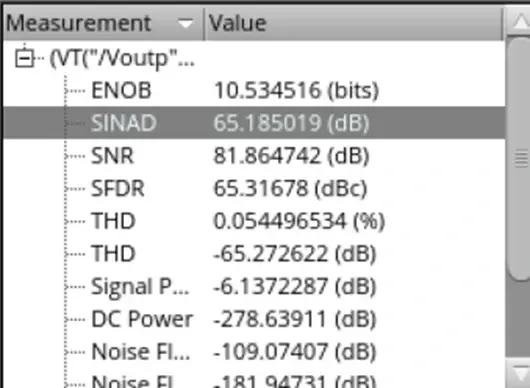

可以看到性能有改善,但还是达不到要求,猜测是其W还不够大,此外M4导通电阻决定了M1和M3的关断速度,增大其W至5u。仿真结果如下所示,终于达到了设计指标。

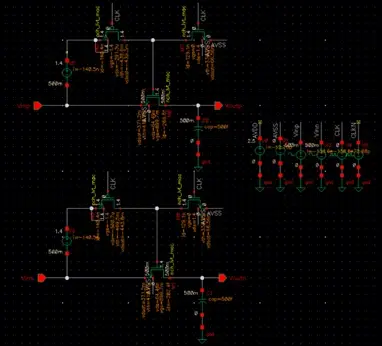

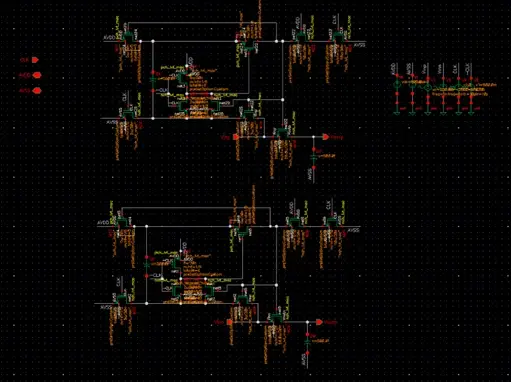

6. 最终电路

现在有几个问题,其一是有些管子的栅源电压或者漏源电压远高于VDD,可能会造成MOS击穿或者影响其使用寿命。例如M4在打开是的漏源电压和M2在打开的时的栅源电压。

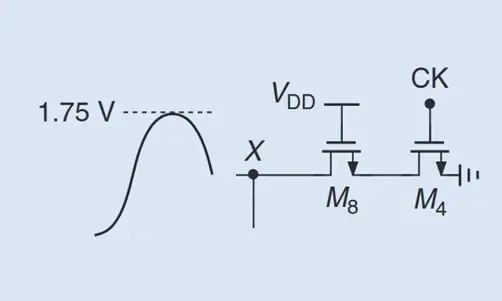

M4的解决办法是加上一个Cascode管来分压,保证VDS4<VDD,且M8自身的VDS最大值为1.75-(VDD-VTH)≈1.05V,因为该回路上多了电阻,几乎时间常数扩大了一倍,故将将M8和M4的W同样增大为10u。

M2唯一的解决办法是让其栅极在采样模式下跟随Vin变化,在保持状态下接到VDD。为此增加了Ma和Mb两个管子。值得注意的是当输入信号Vin较大时Ma的VGS可能较小,使其导通电阻变大影响性能,故增加Mc来帮助传输输入信号。先暂定Ma的W为0.5u,Mb的W为2u,Mc尺寸与M3一致为3u。

最后的电路结构如下所示。

性能下降这么多的原因是因为要经过Mb才能将M2关断,故将Mb提升至6u仿真结果如下,接近设计目标。

故继续将Ma的尺寸提升至2u,M1的尺寸提升至28u,仿真结果如下:

最终尺寸如下所示,W1=28u,W2=6u,W3=3u,W4=W8=10u,M5=M6=5u,WMa=2u,WMb=6u,WMc=3u,CB=500fF,CL=500fF。