自编教材分享:第一章-程序性能优化的意义(一)

本文主要从处理器架构的发展阐述程序性能优化的意义。

程序性能提升的意义

提高生产力水平

提高资源利用率

降低成本

满足时效性

增强用户体验

处理器架构发展

纵观处理器的发展历程,其早期的性能增长基本遵从摩尔定律,但是随着主频的不断提升、芯片上集成的晶体管数的急剧增加,功耗、互连、复杂度也在指数级的增长,此时的摩尔定律不再适用于单核处理器。

单核结构

单核指CPU集成了一个运算核心。单核处理器的性能与主频和每个时钟周期内执行的指令数相关。一般有两种提升单核处理器性能的方法,第一种是提高主频,第二种是提高每个时钟周期内的执行效率。

提高主频

超大规模集成电路工艺的发展,使得单颗芯片上可集成更多的资源,为处理器体系结构的发展提供了源源动力,通过改进处理器体系结构获得更高的时钟频率是单核处理器设计的重要方向之一。

提高每个时钟周期内的执行效率

提高每个时钟周期内的执行效率的方式之一就是采用并行计算,分为指令级并行和数据级并行,指令级并行是指处理器同时执行多条指令,数据级并行是指对程序中的多个数据进行相同操作。

图2列出了部分主流处理器厂商的处理器型号,以及SIMD扩展指令级的名称和特征。

多核结构

多核处理器即在一个单芯片上集成多个处理器内核,其中每个核都是一个独立的物理处理器,多核处理器支持多个线程在多个处理器核上同时执行,使得整个处理器可同时执行的线程数目是单处理器的数倍,极大地提升了处理器的性能。图3为某国产处理器结构。

众核结构

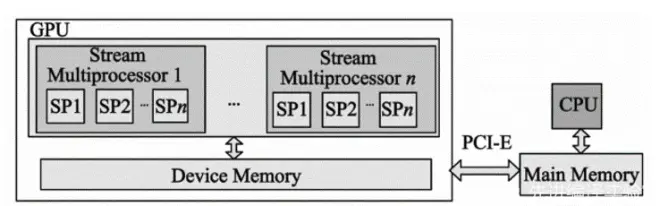

众核处理器由几十到几千个功能较小的内核组成,使用针对更大并行性和吞吐量进行优化的嵌入式处理器,产生大规模的并行数据流,降低完成任务的功耗。众核还能够通过增强的线程同步来解决数据瓶颈的问题。众核与多核之间的关键区别包括处理器核心的数量以及实际的处理器结构。多核处理器一般核心数量较少,同时他们的总线结构也不一样,一个是片上的总线矩阵,一个是片上网络。图4为GPU系统结构。

异构结构

异构多核是指将功能或性能相异的处理器通过一定的互连结构连接起来,一般由通用处理器和专用加速处理器构成,在芯片内面向不同的指令集成了不同类型的计算部件。典型代表为索尼、IBM和东芝联合研发的Cell处理器。

专用结构

专用处理器是通过将硬件架构进行定制并使其具备特定领域应用特征,使得该领域的一系列应用任务都能高效执行,例如在机器学习领域,比较有代表性的专用架构为Google的张量处理器TPU,专用于神经网络运算、神经机器翻译等诸多任务。

参考资料

[1]李明亮.面向多核和众核的跨架构程序移植关键技术研究[D].战略支援部队信息工程大学,2021.DOl:10.27188/d.cnki.gzjxu.2021.000074.

[2]邓豹,孙靖国.国产嵌入式处理器发展综述[J].航空计算技术,2021,51(01):120-124.

课程书籍