Altium Designer 20 19(入门到精通全38集)四层板智能车PC

--------------- 创建工程和元件库 ---------------

工程内容:

- 原理图库:绘制出芯片、元件模型

- 原理图:把原理图库里的原件连接、连线

- PCB库:同理于原理图库,原理图和PCB桥接的桥梁。和PCB实物尺寸是对应的,因此一定要比较精准。

- PCB图:PCB布局布线

- 其他生成文件

创建工程

- 列表中的选项,是各种demo,一般直接default

- 创建原理图库(元件库)

- 创建时不会自动保存空文件,CTRL+S保存、命名

- 新建原理图

- 创建PCB库

- 新建PCB

- 一定要工程的基础上,去建立库和图,不然Free Document下,难以链接和管理

- 右下角Panels按键用法 视图→状态栏 点出Panel,这里也可以选择左侧栏显示的内容,选择SCH Library 则显示原件库列表

元件

- 新建元件,定义其属性 双击或按编辑进行属性定义

- 元件图的内涵:元件库要包含元件边框、管脚(序号和名称)、元件名称、元件说明

- 元件图和实物尺寸不对应,和Multisim相似

画一个电阻

- 放管脚,放的过程中按Tab或者放之后双击 都可以进入管脚编辑(Designator 位号 Name 管脚名称 Symbol栏设置形状,不改变性能,只是从符号上进行说明),为了美观隐藏Name

- 管脚上四个白点:有电气属性,朝向电阻外部,管脚两端是不同的

- 按空格旋转图形90°

- 画出电阻形状(边框):绘制线,同样双击后可以修改属性

- 绘制精度:网格边长是100mil,设置捕捉点的尺度:视图→栅格→设置捕捉栅格(绘制建议设置10mil,放置建议设置1 00mil)

- 复制的快捷操作:选中一些目标,按住Shift拖动

- 元件描述:元件属性中的Description描述,Link放置链接(如网址等)

- 电阻的位号一般写R?,原理图绘制的最后再进行统一位号排序(R1,R2...)

- 封装:Footprint,PCB的封装,可以在原理图绘制好之后,根据实际情况统一去加。现在就加的话,在下面Editor的Add Footprint增加

排针类放置

- 阵列粘贴功能:编辑→阵列式粘贴

从现有的原理图,自动生成一个库

- ?必须是现有的.SchDoc文件吗

- 设计→生成原理图库

- Grouping是在分类 归类设置勾前三个就行

--------------- 原理图 ---------------

打开原理图,SchDoc文件

绘制原理图

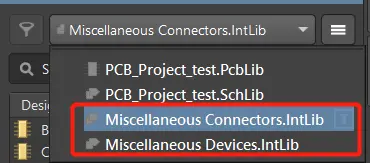

- 右下角Panels→Components,会显示自带的库和自己的库

- 放置器件快捷操作:直接拖动出来

- 一般把所有需要用到的元件先全拖出来(不考虑个数)

- 设置纸张大小:Panels→Properties→Sheet Size

- 复制:框选后按住Shift拖动

- 多个器件对齐:框选→快捷键A 要关掉输入法

- 原理图模块分区:放置→绘图工具→线(空格改变线的走线方式) 是无电气属性的

- 原理图子图:放置→页面符,双击拉到底下sheet entries添加子图引脚

- 放置导线:Ctrl+W 即放置→线

- 放置GND、VCC等

- 更新原理图:更改元件模型后,在SCH Library中右键点击元件→更新原理图,则原理图中会同步更新(在原理图中单独更改了位号和Value,此时更新,则位号不会变,但Value会变)

- 就近原则:元件尽量靠近了

- NetLabel(引脚说明):放置→网络标签,标签下脚和引脚端点需在同一点

- 器件位号Designator编辑(如R?):工具→标注→原理图标注(快捷键T A A)

- Value值:如电阻下面写的1K,未设置则会默认为Design Item ID

- 封装模型Footprint的意义:原理图怎么映射到PCB

- 封装管理器:工具→封装管理器 按住Shift再点,可以扩选

- 报错设置:工程→工程选项,Error Reporting是错误表,在这设置各种错误的报告格式

- 编译:工程→Compile PCB....(第一个)

- 根据元件库同步更新:AD中如果修改了元件库,原理图中不会自动更新,在工具→从库更新中,选择要更新的元件进行更新

常见报错

- Duplicate Part Dsignators位号重复

- Floating net labels/ Floating power objects 前者是NetLabel位置错了,后者是GND VCC之类的悬浮未连线

- Net with only one pin单端网络,一个引脚的NetLabel没有对应到其他引脚,说明是单端的,不一定有错

- Panels→Message 可以查看Error

- 通用No ERC符号:放置→指示 用来说明引脚不连接导线

----- PCB封装库的创建和调用 -----

PCB封装是原理图到实物的映射,PCB封装尺寸等于实际尺寸,要精确设计

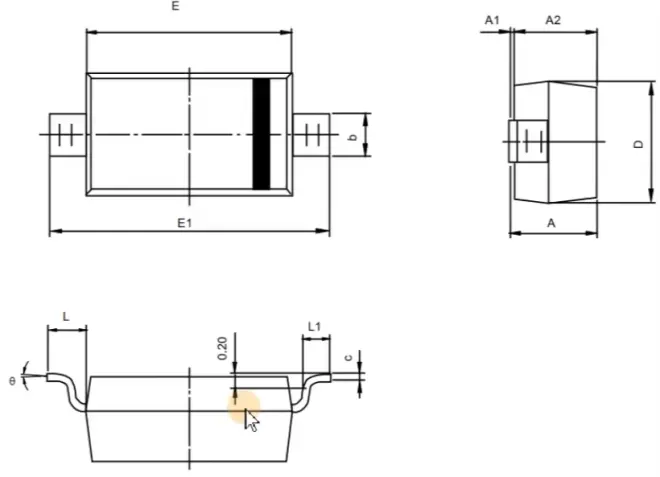

常见CHIP:电阻容 SOD 二极管

模仿根据规格书封装尺寸实例,画一个二极管封装

焊盘宽度d,管脚长度L... 每一个尺寸在datasheet中都会给出建议的范围(可以直接选最大值)

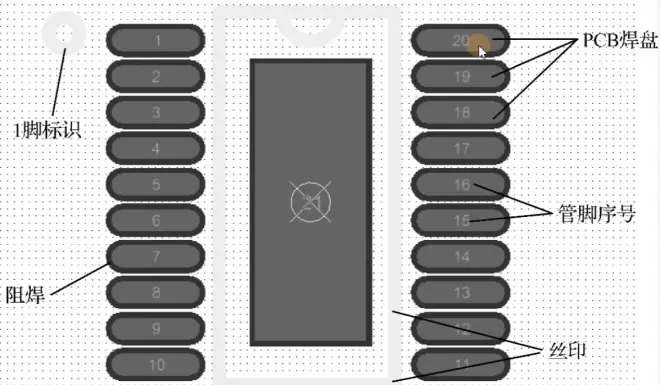

完整PCB封装需要的元素

- 管教序号和原理图是对应的,直接交互

- 丝印:实物本体大概的范围

- 1脚标识:定位器件方向,比如电容正反端

- 阻焊:图中黑色的外框,防止绿油溅到焊盘上(PCB板表面的绿色绝缘油墨)

创建常见chip封装

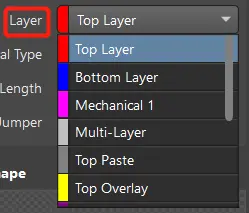

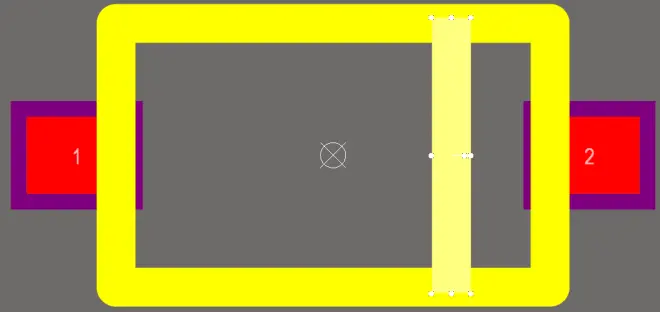

1.画焊盘Layer:通孔Multi-layer,表贴top layer

- 坐标轴上精准移动:m→通过X,Y移动选中对象

- 测量图纸上的距离:Ctrl+m,s hift+c撤销距离标记

- 移动图纸中心圆圈到中间:编辑→设置参考→中心

2.画丝印top overlay:线条,在线条属性的layer中选top overlay

- 以参考点进行复制:选中→Ctrl+C→选择参考点→Ctrl+V

- 镜像:X

3.画1脚标识(极性):放置→填充 放置了填充的一侧是负极

4.画阻焊:放置焊盘后默认有,不用管

5.画引脚号

IC类封装:

- 特殊粘贴:引脚很多的情形 Ctrl+C→选中被复制物中心→编辑→特殊粘贴→阵列粘贴→设置完后点击被复制物中心(注意原位置会重复一个)

生成PCB库:

从现成的PCB图中提取出用到的PCB库,设计→生成PCB库,再拷贝到自己的库,也可以PCB图中选中器件Ctrl+C,直接到自己的库Ctrl+V

----- 网表导入及PCB整体规划 -----

网表导入(从原理图转移到PCB图)和报错:

- 在PCB图选 设计→Import;或者在原理图选 设计→Update。 这时会显示现有PCB图和原理图的比对。执行变更后,器件根据原理图被导入到PCB图

- Add Rooms:导入时,每张原理图会有一个红色框,在导入界面拉到最底下,去掉Add Rooms的选项,则不出现。

- 绿色报错:初导入到PCB图,绿色是出错的意思,因为违反一些规则(工具→设计规则检查:先只保留电气性能Electrical的检查)

- 报错更新:工具→复位错误标志(所有绿色会消失,若还有绿色,会在移动后出现

- 把器件全部放到一个区域内:框选所有器件→工具→器件摆放→在矩形区域排放

- PCB中圆圈圈在一起是短路提示

PCB大小设计

- 工具→器件摆放→在矩形区域排列,排放成一个矩形

- 在mechanical1层,画一个矩形把所有器件圈起来,大小比器件矩形稍大一些(参考长宽都多出15%)

- 将原点位置放置在PCB左下角:编辑→原点→设置,

- 查看属性时,ctrl+Q在mm和mil之间切换,以mm为单位取个整数

- 裁剪板框:选中所有mechanical1边框(按住shift选),设计→板子形状→按照选择对象定义

- 放置线性尺寸,看PCB上的距离(在Unit设置成mm),把尺寸取整数:放置→尺寸→线性尺寸

- 放置固定孔(板子四角的圆孔,参考:xy轴都离边5mm):选中器件,按m(移动)→通过x,y移动所选对象

PCB板层级

- 2层:默认是2层,有Top layer和Bottom layer

- 4层:比如多一个地层和电源层,设计更容易,贵,信号质量高

- 修改层数:设计→层叠管理器;右键→insert layer below;signal是正片层,plane是负片层,core是芯板,Pregreg是pp片;正片层和负片层:正片,有线则导电(有Cu),负片,没线的地方有Cu;top overlay丝印层;top solder阻焊层。

- 层命名,如GND02,02表示在由上到下第二层

- 单层显示:shift+s

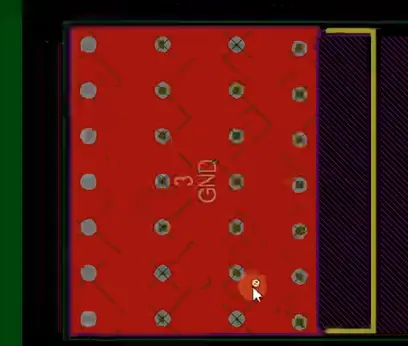

- 在负片层,画出闭合空间,双击闭合空间连接到网络,通过连到不同网络进行分区

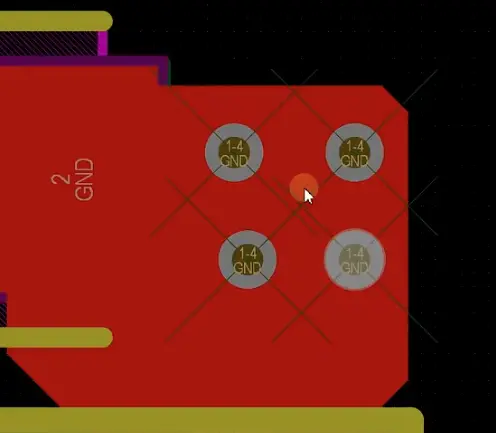

- 负片层指定网络后,只有连接到指定网络信号的过孔才能与该负片层相连。比如GND02指定了网络GND,网络GGND和GND的过孔在GND02层显示如下,GND圆圈是不封闭的,成功 连接到该层,而GGND是封闭的,未连接到该层。

快捷键设置

- 如何设置快捷键:在顶侧选项中,按住ctrl点击对应命令

- 下图,浅色需设置,深色是默认;

- 器件排列离散指的是对选中器件框选排列(F6占用,设成F9);

- 线(框)选:线(矩形框)触碰到的物体被选中,按s可以调出该命令

- 删除网络(布线→取消布线→连接):多段走线一根根删麻烦,一次性删除相连的布线

- 物理选择:选中物理上被连接到一起的器件

- 忽略障碍物:将走线方式切换到“忽略障碍”,采用的方式在右上角齿轮→PCB Editor→Interactive Routing→布线冲突方式,保留前3

- 网络显示关闭:N,网络指的是器件之间的白色连线

------- 信号分类和规则设置 ------

类:

- 设计→类别,对信号进行分类,Panels→PCB

- 对信号线和电源线进行区分,①隐藏电源线可以在布线时看出信号走向;②电源线布线时加粗

- 更改类内信号颜色:右键→Change Net Color,右键→显示替换→选择的打开

规则设置:

- 设计→规则

- Electrical→Clearance:间距规则

- Routing→Width:线宽规则

//可以自己新建规则,并设置其适用对象(层、类、信号等),对同一个网络有多个规则对应,在下方优先级按钮进行优先级设置,并注意在这里勾选规则使能

- Routing→Routing Via Style:过孔规则。

//经验上,外圈大小(过孔直径)是内圈大小(过孔孔径)2倍加减2mil以内。

//信号线可以孔小,方便走线,电源线需孔大,减小阻抗

//默认过孔大小不会随规则设置变化,需要在设置(右上角齿轮)→PCE Editor→Defaults→Via里面修改,过孔盖油默认大小也可以在这里设置,Solder Mask Expansion栏,设置后勾选Tented

- Plane→Power Plane Connect Style:负片层焊盘和过孔

- Plane→Power Plane Clearance:负片层反焊盘间距,在负片层焊盘和周围铜之间的距离(推荐8mil)

- Plane→Power Plane Clearance:正电层焊盘规则

//正片层用十字连接还是全连接:全连接时锡膏散热凝固过快,难以手焊(现在一般都是回流焊),但载流特性好;过孔通常采用全连接

//点开“高级”,可以对通孔焊盘、表贴焊盘和过孔分别设置

- Manufacturing→Silk To Solder Mask Clearance:丝印和阻焊的间距(推荐2mil)

//阻焊是防止油墨覆盖的,丝印是油墨,刷在PCB板上,因此下图中只能看到蓝色圈出部分,看不清位号

- 设计规则检查(工具栏)和规则(设计栏)是对应的

- PCB各层功能介绍:https://mp.weixin.qq.com/s?__biz=MjM5MTI3NzY2Mg==&mid=2651499146&idx=6&sn=38b709f27506c20fd6c919964f472add&chksm=bd49fdbb8a3e74ad5c03dd249e5a697042a640d507a1cb89925603db18a44f9247c0e7dd4242&scene=27

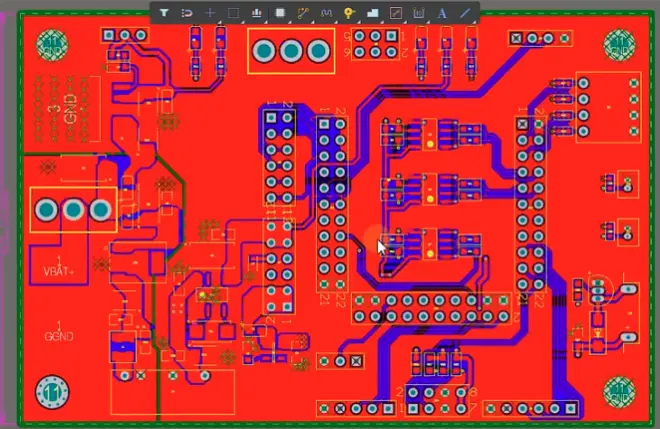

------- 绘制PCB:① 器件布局 ------

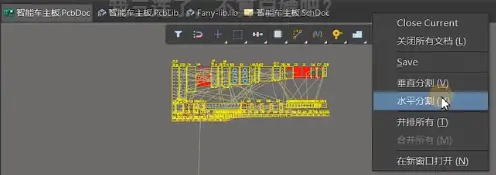

- 页面分屏:右键→水平或垂直分割,一侧看原理图一侧看版图

- 在原理图中阔选的器件,在版图中同步选中:需要手动开启,工具→交叉选择模式。

- 基于此,把原理图中各个模块在版图中分开放置

- 交叉探针:T→C,原理图(PCB)中选中的器件,在PCB(原理图)中找到,按shift+c取消高亮。

- 信号分类和显示:设计→类,在此处对所有信号分类;右下角Panels→PCB,右键点击类→连接→显示或隐藏;

- 先大后小的原则:先大模块再小模块

- 就近原则

- 联合:类似visio的组合,扩选→右键→联合

- 在类中隐藏电源线,观察信号流向,根据信号线就近布局模块,布好再看合不合理

- 拨码开关习惯放右侧,惯用右手;LED习惯放上侧

- 更改位号位置:快捷键a→定位器件文本

- 切换3D视图:Ctrl+d→View Options

- 背面也放器件会增加造价

------- 绘制PCB:② 善孔和铺铜 ------

善孔

- 打孔要在走线前完成:减小后期走线工作量

- 就近打孔可以缩短回流路径,提高信号质量

- 走线尽量垂直地从焊盘中间引出

- 长线先就近打个孔,后面再处理

- 推荐所有过孔都盖油

- 信号走线尽量少打孔:①延长了路径;②增加阻抗

铺铜

- 主要用于电源模块,本质和导线是一样的

- 铺铜后可以多放一些孔来增加传输特性

- 散热焊盘放大量用于散热的孔

------- 绘制PCB:③ 布线和表层灌铜 ------

布线

- 先处理信号走线,再处理电源走线

- 信号走线尽量少打孔

- 先连好线,不管规则检查,后面再调整

- 负片层的分割:把模拟和数字隔开(推荐宽度20mil)

- 按住ctrl布线,对线进行修正

- 布线尽量均匀

表层灌铜

- 表层灌铜(包括Top和Bottom):可选,参考论坛 https://mp.weixin.qq.com/s?__biz=MzA3OTM2NzUxOA==&mid=401983924&idx=6&sn=34975301083b9ba919a016706d82a470&chksm=0db5f5853ac27c93d84ae6bf327603f64d52ab0ca3537d8a56176d44b418fc11792d4e879b7f&scene=27

- 表面灌铜后,要把尖角铜皮去掉

------- DRC检查 ------

设计规则检查

- 工具→设计规则检查

- 在Report Options中选择创建报告文件

- 先勾选Electrical的所有内容,运行DRC

- Panels→Message 查看报错内容,双击后跳转到对应位置

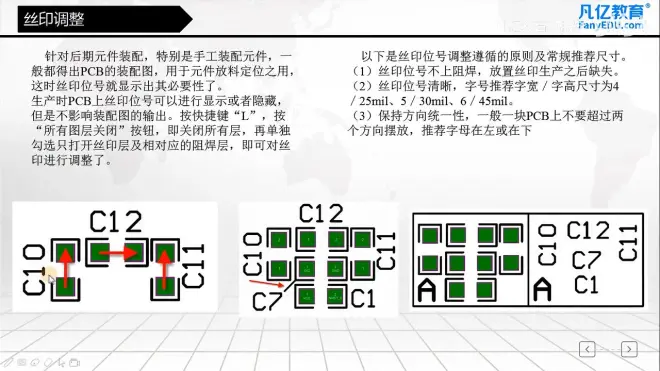

丝印调整

- 选中所有同类丝印:右键一个丝印→查找相似对象→Object Specific里,String Type改成Same

------- 文件输出 ------

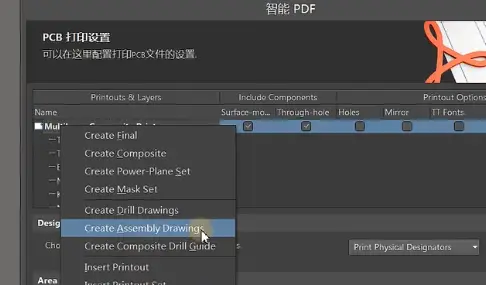

装配图输出

- 简略版:文件→装配输出→Assembly Drawing,分为表层和底层,点击打印,选择PDF输出,这样生成的比较简略

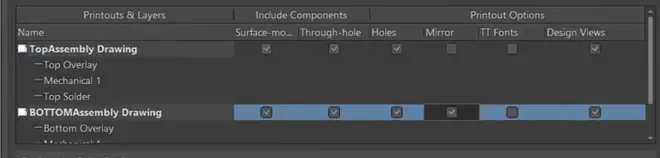

- 完整版:文件→智能PDF→当前文档→不导出BOM→右键→Create Assembly Drawings→yes

// 保留顶层和底层,双击层名去编辑打印内容,保留丝印层(Overlay)、板框(Mechanical1)、阻焊(Solder)

// 进行如下勾选

// Area to print选择Entire Sheet,进入下一页

// 附加信息栏目,不产生网络信息,右侧可以选择颜色模式,进入下一页,如下勾选

BOM表输出

- 报告→Bill of Materials

- 右侧properties下,选中Columns栏,在下方选择要打印的内容,通常保留Comment Designator Footprint Quantity

- 右侧properties下,选中general栏,下方可在template中选择模板

Gerber等文件输出

- 工作路径下的History和Project Outputs文件夹可以先删掉

- 文件→制造输出→Gerber File

// 通用:单位英寸,格式2:4

// 层:绘制层→选择使用的,镜像层→全部去掉,右侧机械一层添加到所有层输出(板框),可以勾上

// 钻孔图层:钻孔图勾选输出所有使用的钻孔对,钻孔导向图输出所有使用的钻孔对

// 光圈:一般默认就行

// 高级:胶片规则里全部加个零,增大画布面积,其他默认

- 钻孔文件:文件→制造输出→NC Drill Files,同样选择英寸、2:4

- 坐标文件(用于贴片的):文件→装配输出→Generates pick and place files,英制单位,文本格式,左边勾选Center-X, Center-Y, Comment, Designator, Footprint, Layer, Rotation

- IPC网表:文件→制造输出→Test point Report→报告格式选IPC,用于板厂对开短路的再次检查

- 生成的cam文件都可以删掉

文件整理

- 文件位置:前面生成的所有文件中,bom和装配图在工程目录里,其余(Gerber等文件)在Project Outputs for...子目录里

- History文件夹没什么用,可以删

- 坐标文件默认名为Pick Place for... 改名为坐标文件

- 创建名为CAM的文件夹,发给板厂;含上一节“Gerber等文件输出”里的所有文件

- 创建名为ASM(装配)的文件夹,发给贴片厂;含BOM表,装配图,坐标文件,钢网层(Gerber文件中的GTP和GBP,即Gerber Top Paste和Gerber Bottom Paste)