3.13插值滤波器设计--明德扬科教2(mdy-edu.com)

接3.13插值滤波器设计--明德扬科教1(mdy-edu.com)

第5节 简化版步骤分享

这里依旧会分享简化版的步骤,方便掌握基础原理后进行反复操作复习。

5.1 设计实现

5.1.1 顶层信号

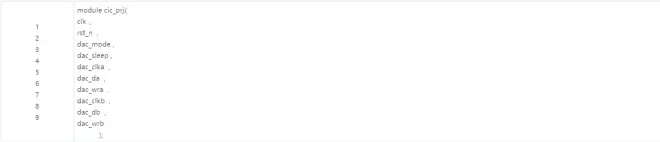

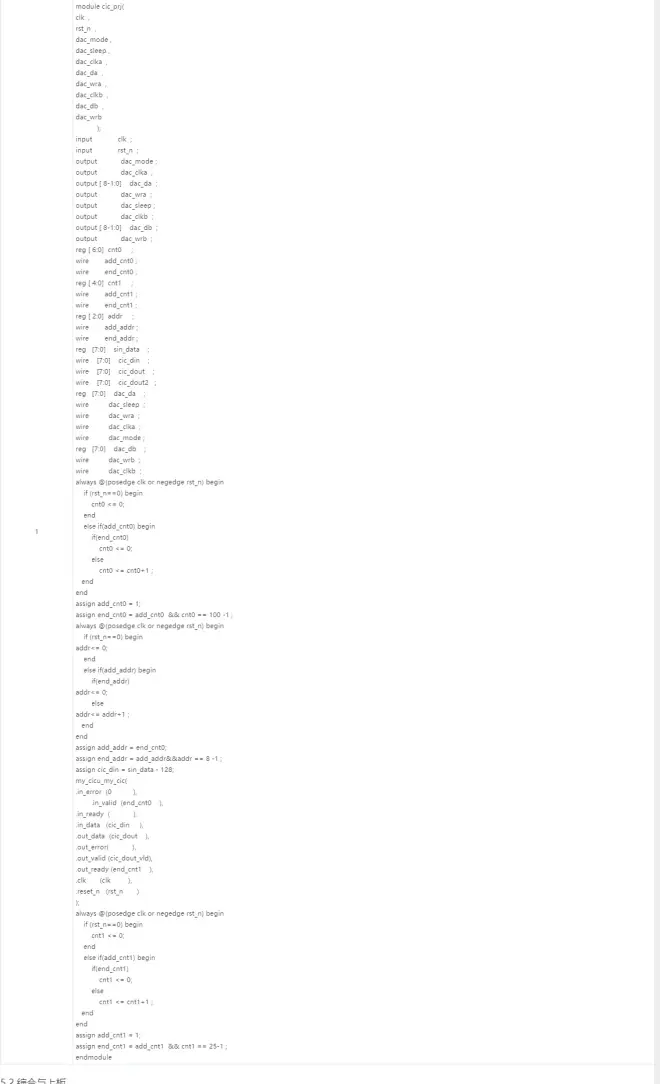

新建目录:D:mdy_bookcic_prj。在该目录中,新建一个名为cic_prj.v的文件,并用GVIM打开,开始编写代码。

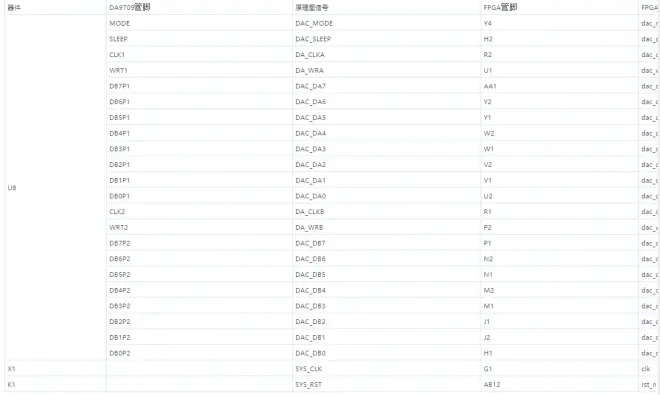

分析设计目标确定顶层信号。信号和硬件的对应关系图见下表所示。

表3.14 - 2信号和管脚关系

写出顶层信号。

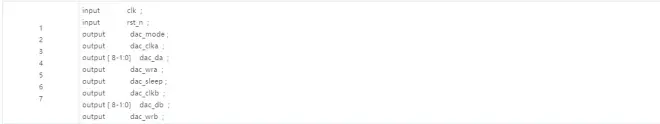

声明输入输出属性。

5.1.2 正弦信号设计

设计正弦信号sin_data信号:

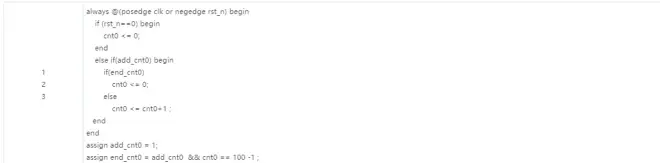

设计表示输出值的计时器cnt0:

设计addr信号:

CIC滤波器设计

步骤一:新建FPGA工程

打开软件“Quartus”,点击“File”菜单下的“New Project Wizard”,如下图所示。

错误!未找到引用源。 12 QUARTUS新建工程命令界面

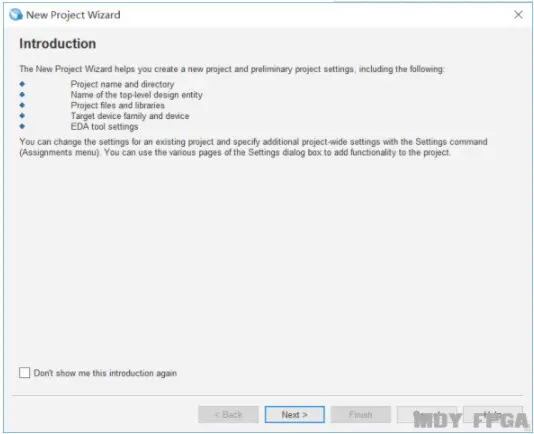

弹出“Introduction”界面后点击“Next”:

图3.14-41QUARTUS新建工程介绍界面

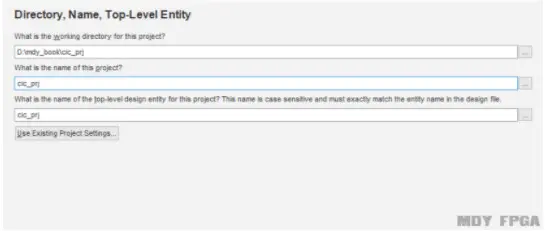

设置工程目录(目录为D:mdy_bookcic_prj,工程名和顶层名为cic_prj)后点击“Next”。

图3.14-14QUARTUS设置路径和名称界面

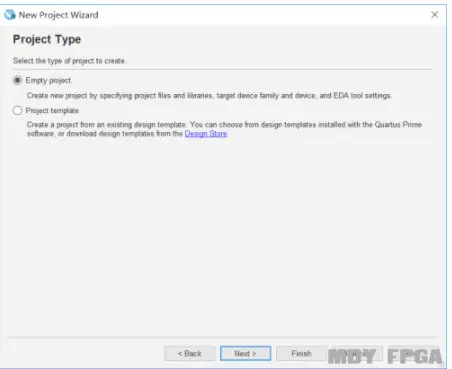

选择“Empty project”后点击“Next”。

图3.14-42QUARTUS设置新建工程类型界面

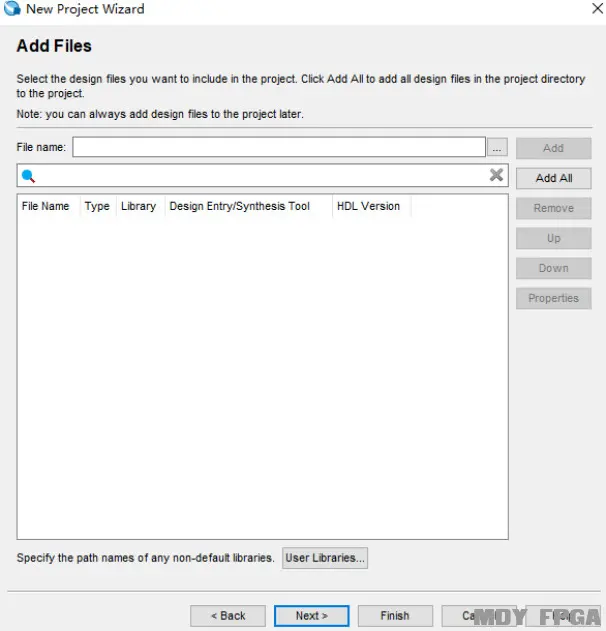

此界面不选择任何文件,点击“Next”。

图3.14-16QUARTUS添加文件到新工程界面

对芯片型号进行选择,在“Device family”选项中选择“Cyclone ⅣE”,“Available devices”选项下选择“EP4CE15F23C8”,随后点击“Next”。

图3.14-17 QUARTUS设置新工程的芯片类型

步骤二:FPGA生成CIC IP核

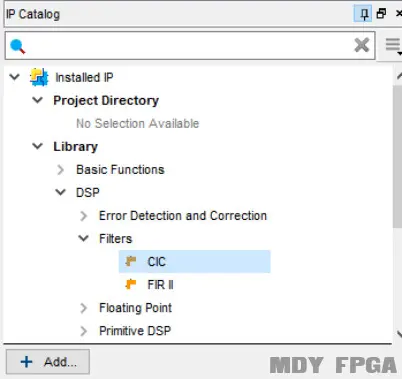

建立工程后,在软件“Quartus”的“IP catalog”这一界面中选择“DSP”目录下“Filter”的“FIR II”选项,如下图所示。

图3.14-18 IP Catalog中查找CIC IP核

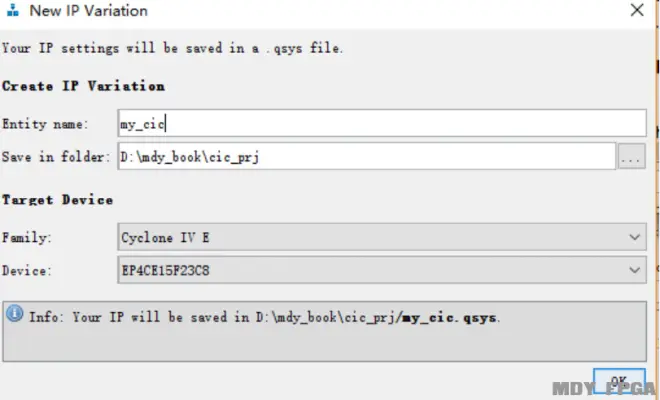

选择路径为D:mdy_bookcic_prj,在“entity name”处填写my_cic,随后点击“OK”:

图3.14-19设置CIC IP核的名称和路径

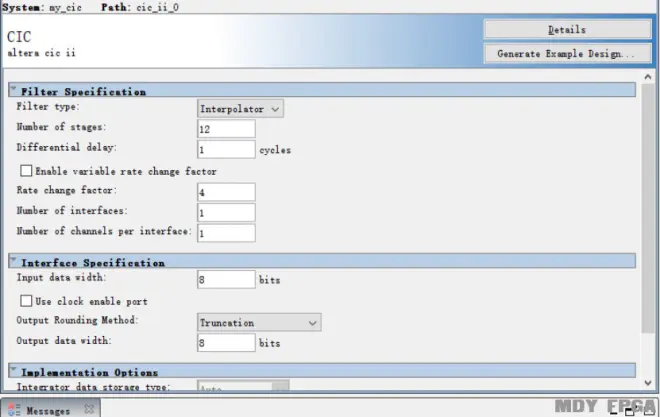

随后对IP核类型进行设置。“Filter Type”选择“Interpolator”,“Rate change factor”处填写4,“output Rounding Method”选择“Truncation”,“Output data width”选择8,其它选项默认后点击“Generate Hdl”。

图3.14-20CIC IP核的设置界面

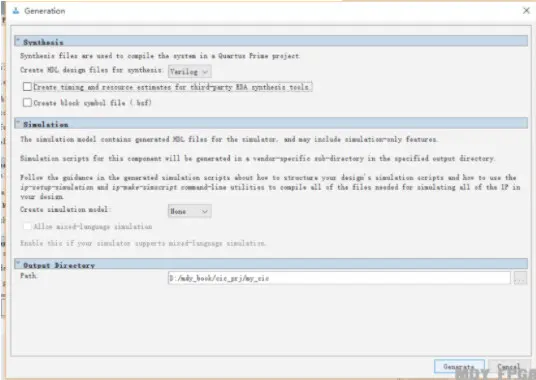

选择文件为“Verilog”文件后点击“Generate”。

图3.14-43设置CIC IP核的文件类型和路径

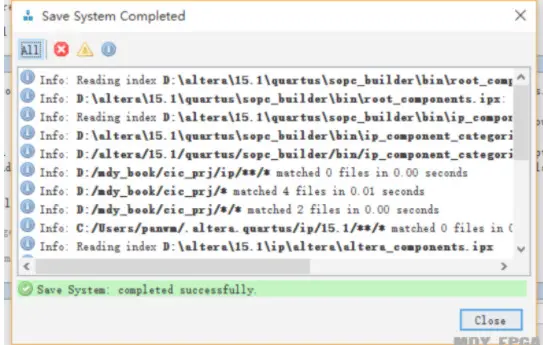

出现下图提示则表示CIC IP核生成成功,点击Finish关闭CIC滤波器生成窗口。

图3.14-22 CIC IP核生成成功提示界面

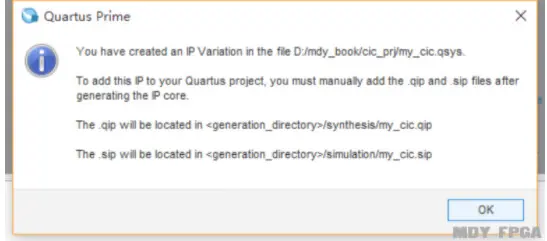

如果出现以下提示,就表示需要手动将刚才生成的IP核加到本工程。

图3.14-23将CIC IP核加到新工程提示

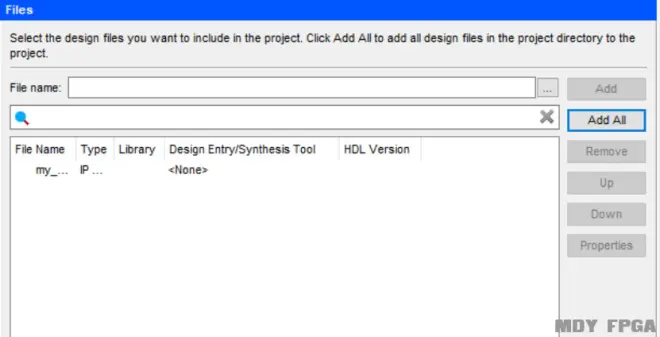

此时需要在“Project”菜单中选择“Add/Remove File to Project”,随后弹出文件窗口。

图3.14-24手动添加CIC IP核到工程

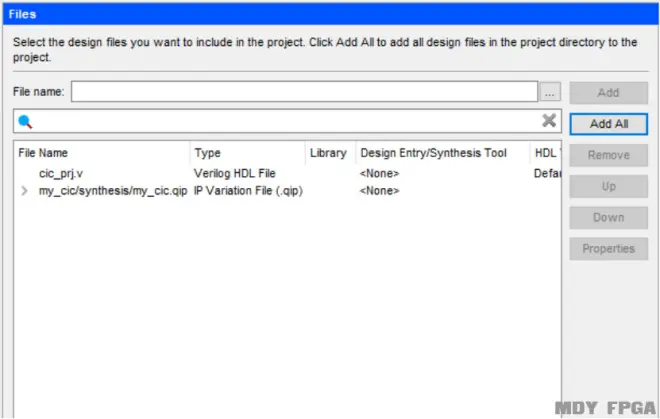

点击右上角的

按钮,在弹出来的窗口中双击选择D:mdy_bookcic_prjmy_cicsynthesis目录下的my_cic.qip文件。点击“Add”添加成功后关闭本窗口。

图3.14-25添加CIC IP核文件到工程

步骤三:例化CIC IP核

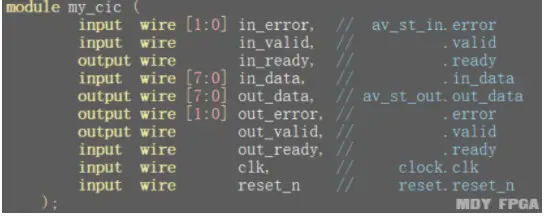

打开D:mdy_bookcic_prjmy_cicsynthesismy_cic.v文件,生成的CIC IP核文件如下图所示。

图3.14-26 CIC IP核的模块和输入输出信号

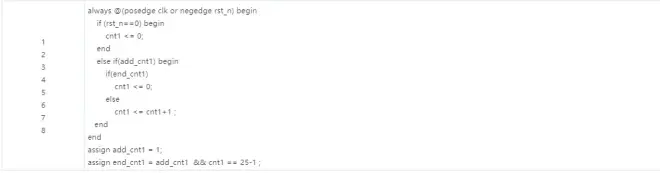

设计表示IP核输出的计数器cnt1:

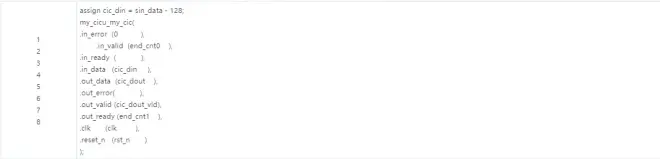

将CIC IP核例化:

5.1.4.DA接口信号设计

设计信号dac_da:

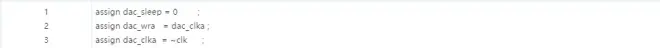

设计信号dac_sleep、dac_clka、dac_wra:

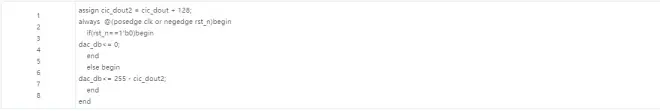

设计信号dac_db:

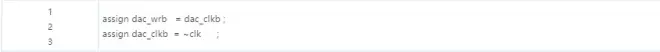

设计信号dac_clkb,dac_wrb:

至此,模块主体已经完成。接下来将module补充完整。

5.1.5 信号定义

首先来定义信号类型。cnt0、add_cnt0和end_cnt0的信号定义如下:

cnt1、add_cnt1和end_cnt1的信号定义如下:

addr、add_addr和end_addr的信号定义如下:

sin_data的信号定义如下:

cic_din的信号定义如下:

cic_dout的信号定义如下:

cic_dout2的信号定义如下:

dac_da、dac_sleep、dac_wra、dac_clka、dac_mode的信号定义如下:

dac_db、dac_wrb、dac_clkb的信号定义如下:

在代码的最后一行写下endmodule

至此,整个代码的设计工作已经完成。完整版的工程代码如下:

5.2 综合与上板

5.2.1 添加文件

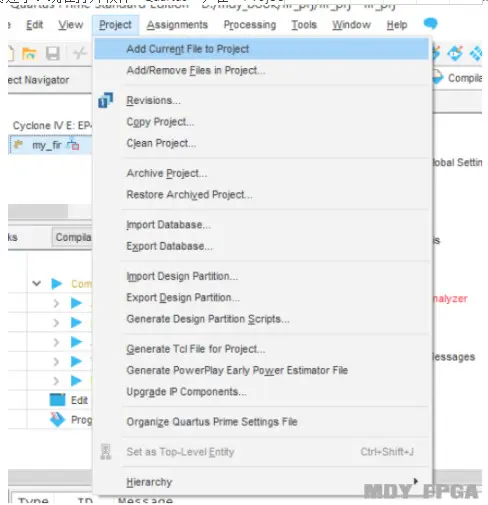

上一节中已经介绍了新建工程的过程,这里就不再赘述了。现在打开软件“Quartus”,在“Project”菜单中选择“Add/Remove File to Project”,弹出文件窗口。

图3.14-28添加文件命令界面

点击右上角的

按钮,在弹出来的窗口中,双击选择D:mdy_bookcic_prj目录下的cic_prj.v文件。点击“Add”添加成功后关闭本窗口。

图3.14-29添加文件成功界面

5.2.2 综合

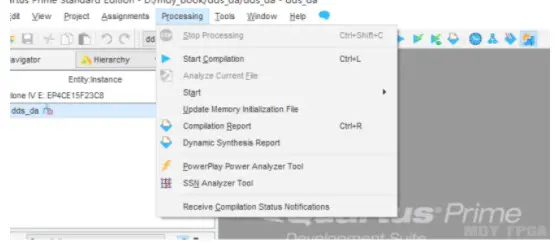

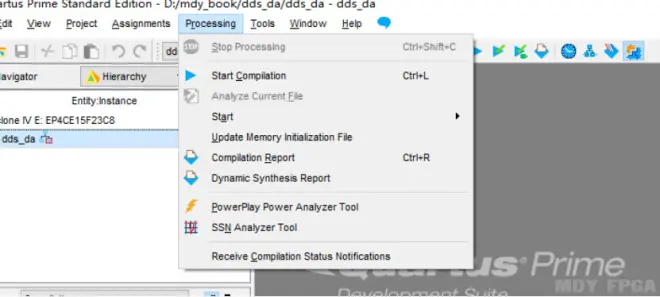

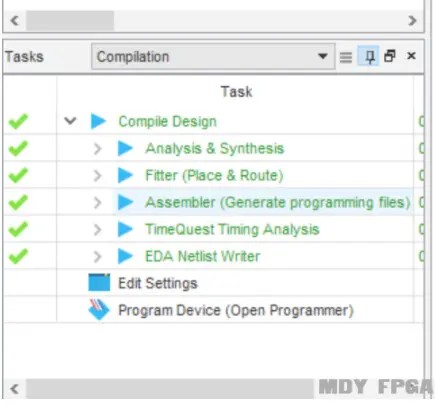

在菜单栏中选中Processing,然后选择Start Compilation,开始对整个工程进行编译和综合。

图3.14-30编译命令界面

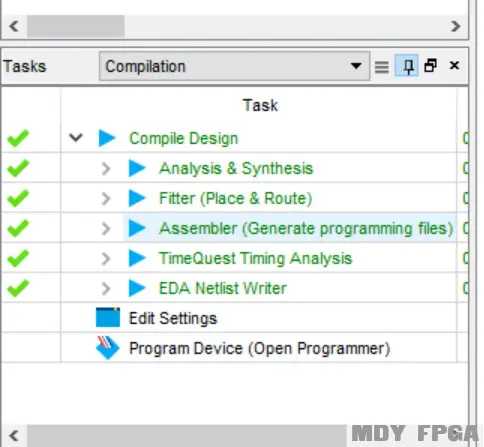

当出现下图的界面,则就说明编译综合成功。

图3.14-31 编译成功界面

5.2.3 配置管脚

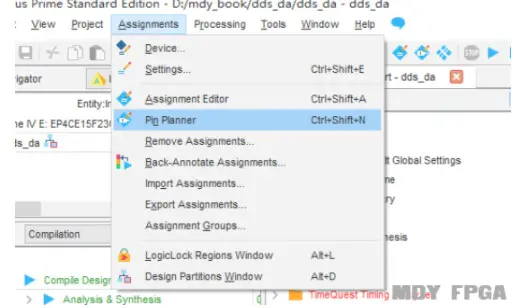

配置管脚界面如下图所示,在菜单栏中选中“Assignments”,然后选择“Pin Planner”,随后就会弹出配置管脚的窗口。

图3.14-32 配置管脚命令界面

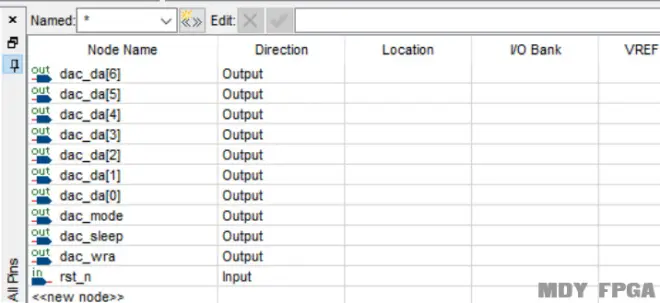

在配置窗口“location”配置管脚,配置完成关闭“Pin Planner”即可自动保存配置信息。

图3.14-33 配置管脚界面

5.2.4 再次综合

再次打开“QUARTUS”软件,在菜单栏中选中“Processing”,然后选择“Start Compilation”,再次对整个工程进行编译和综合,如下图所示。

图3.14-35 编译命令界面

当出现图3.2-19QUARTUS编译成功标志则说明编译综合成功。

图3.14-36编译成功界面

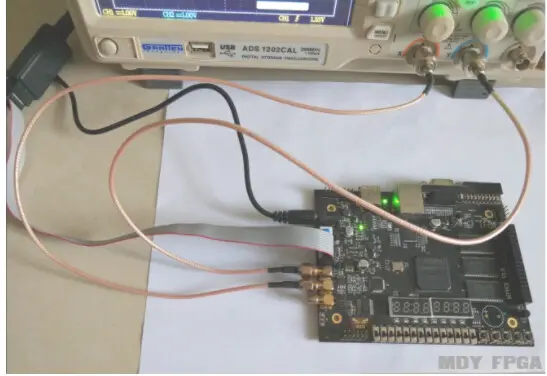

5.2.5 连接开发板

完成编译后开始进行上板调试操作,开发板连接方式如下图所示。将电源接上开发板,USB BLASTER一端连接到JTAG插口,另一端连到PC的USB接口。将开发板上的AD接口和DA与示波器的两个通道相连,连接完成后再将电源打开。

图3.14-37教学板连接示意图

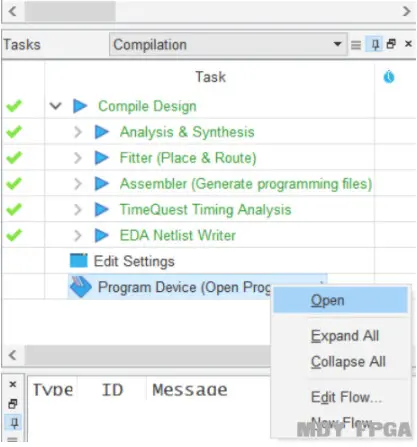

5.2.6 上板

在“Quartus”的“Task”窗口中,右键“Program Device”选择“Open”进入烧录界面,如下图所示。

图3.14-38打开配置程序命令

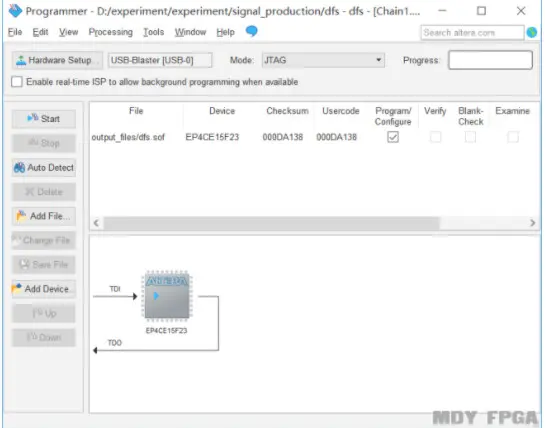

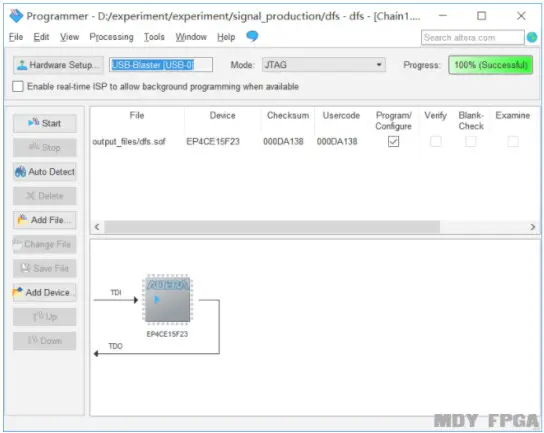

默认会选中文件output/fir_prj.sof,在Hardware Setup旁边会显示USB-Blaste,如下图所示。

图3.14-39 配置程序界面

进度条中提示成功后可在示波器中观察相应现象。

图3.14-40 配置成功界面

第6节 扩展练习

至此,整个插值滤波器设计就分享完毕了,学会了整个设计之后可以展开思考,基于原理不变的情况下多做一些尝试,比如尝试输出三角波,这样帮助同学们更深刻的掌握本案例。也欢迎有更多思路和想法的同学在至简设计法论坛上进行交流讨论。