【知乎】Intel X86服务器架构(七)IMC和IIO

Intel X86服务器架构(七)IMC和IIO

雪瀑牵裳

IT 老棒槌

41 人赞同了该文章

正式迎来了春暖花开的日子。

先是看着柳树从鹅黄变得碧绿,然后又看到一丛丛的迎春簇拥着,形成明黄的花海。

当我从技术大坑里灰头土脸的爬出来,已然看到小叶李和美人樱给马路增添了第一抹红,让我站在人生的交叉路口,恍惚。

暖洋洋的日光,让人内心骚动。嗯,又是一个踏青烧烤的好时候了。

先泡上一杯咖啡,就在这暧昧的阳光下,我们开始intel x86架构的第七篇,也就是skylake CPU内uncore部件讲解最后一部分:IIO和 IMC。

回头看看intel x86架构系列的四,五,六篇以及当前这第七篇,我用了四个篇幅,罗列了skylake CPU 内部结构的各个PCI组件。从这些组件在SKX CPU内部架构中的位置,简单讲解的各个组件的功能。

——其实这四篇的内容就像流水账一样,相当的枯燥。每次提笔,我都犯愁该如何下笔。年轻时我玩的时小型机和集中式存储、而不是x86出身啊,所以基本功不扎实啊。

当我捏着鼻子将所有的部件都介绍了一遍后,线下我将重新review一遍之前的几篇,看看是否有之前挖的坑却还没填上的。若是没有留下的坑,从第8篇起将会从功能的角度,把这些部件都串接起来。

所以说,从之前到现在,流水账一般的介绍,是为了给后面功能的展现打基础。(——此时,应该有个庄大户边剔牙边嘬个牙花子说了:你看,你还是摆脱不了理科男的小农思维。:))否则,后续篇幅一涉及到某某的啥寄存器的第几位,我还要大篇幅的介绍某某是个什么玩意儿。

一、重温SKX CPU架构

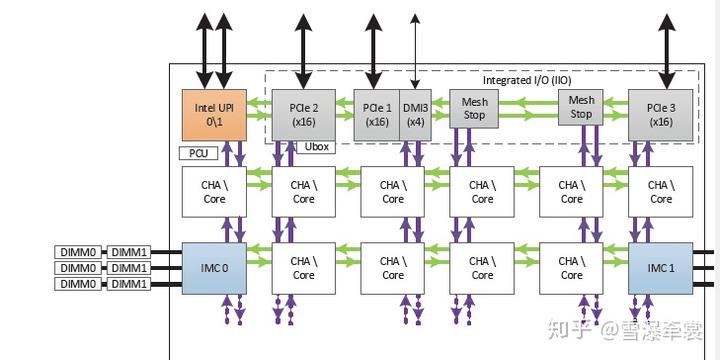

如上图,在一个skyX CPU Socket 内部,各个部件的名称:

Cores

CHA

UBOX

PCU

IIO

IMC

上上篇已经讲完了Cores,CHA,以及寄存器。

上一篇已经讲完了UBOX和PCU。

本篇来认识一下IMC和IIO。

二、IMC

IMC 的全称是Integrated Memory Controller,集成内存控制器。IMC是内存通道控制模组。一般来说和CPU socket的CHA进行通信。

我的Intel X86架构系列开篇就说过一句话:“不知从何时,网上的资料就有一种说法,intel CPU 已将系统板上传统意义的北桥(north bridge)包含在CPU内了。”其实网上这句话的意思应该是:系统板的北桥最重要的功能是内存控制器;而现在的Intel CPU已经将内存控制器集成到了内部。

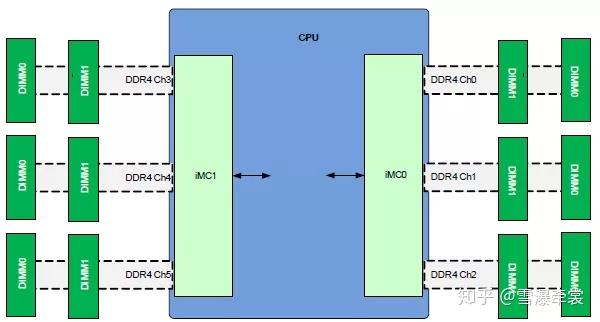

所以,当我们去掉CPU内的其他模组、放大CPU的IMC区域,就会看到以下画面:

图片说明:

1、 SKX CPU正常配置,一个socket里有两个IMC,编号为IMC0,IMC1;(到目前为止,我只在某些Intel 特偏门的诊断案例总结里看到单个IMC的信息,但是现实中我所见的SKX CPU 都是两个IMC)

2、 每个IMC 连出三个 channel;

所以正常情况下,SKX CPU共有6个channel。Intel对6个channel的标识是:

IMC0 channel0;

IMC0 channel1;

IMC0 channel2;

IMC1 channel0;

IMC1 channel1;

IMC1 channel2;

当然有的时候,尤其是在CHA相关的寄存器中,intel CPU寄存器值或intel内部文档中,有时候是这么标识 channel的:

物理channel0;

物理channel1;

物理channel2;

物理channel3;

物理channel4;

物理channel5;

以上两种标识方法,对比同一个位置channel的两个ID,其实也好理解。

注意一点:上边第二种标识中,我用了物理 channel。之所以用“物理”二字,是因为,在某些CPU寄存器里(用于address decode的某些寄存器) ,存在着 ”内存逻辑 channel id”值。而“逻辑channel id”和“物理channel id”的值,是不同的!

3、 每个channel里,有两个dimm槽位,分别为dimm0,dimm1;

关于这一点,我也见到过些阉割设计的。例如我曾经看到一款的skylake服务器,这款服务器的每个channel只有一个dimm槽位。

——可惜这种内存架构,我遇见是在数年前。那时,我还在为海水司的破刀片,破以太网交换模块的破方案焦头烂额,海水司哪有什么像样的方案啊????所以那时没空搞明白超微这个IMC channel架构究竟是怎么回事儿。

4、 某些服务器厂商,还经常按照自己的规则来定义主板的内存丝印编码,例如:

DIMMCPU0A0

DIMMCPU0A1

DIMMCPU0B0

DIMMCPU0B1

… …

服务器厂商自己定义的这个内存标识丝印,与上面2、3 所述的intel内存标识,二者之间的对应关系,本应该能通过正常的思维来推断的。

但是,有时候海水司某些研发的思维,还真的反人类。某些拓扑,不按规矩出牌还美其名曰:技术保密。

呃,所以真的印证了那句话,你以为你以为的不见得就是你以为的。这个对应关系还是拿到白纸黑字的对应表才能让人安心啊。

5、 此处挖一个技术小坑。

在SKX CPU里,当出现了内存错误导致的MCE以后,若只通过MCE log(其实就是MCA相关MSR寄存器值),我们只能定位出错的 IMC channel,而无法定位channel下的某个dimm;

这是由于MCA 寄存器的定义导致的。——我在这里先挖个小坑,我将会在后续的intel error handle architecture章节中具体叙述原因。

在这里注明这一点,是因为,海水司提供的所谓的离线诊断工具或云诊断工具啥的,有时候还居然能莫名其妙的根据MSR的寄存器值,无理的解析出了dimm的位置,神奇啊!所以我一直不相信海水司的这些“诊断神器“的,真的不靠谱啊。我还是习惯对着一个个寄存器的的值,转换成2进制,然后一个bit一个bit的手撸。虽然慢一点,但是安心。例如公众号最临近发的那篇番外《如何从服务器寄存器日志诊断到物理部件》,就是一次手撸的全过程。

好的,IMC本身的讲解,先讲到这里。

然后我想说,其实从数据流上说,IMC应该和CHA放在一起讲。因为当core 里的transaction需要读取数据的时,数据读取的寻址的方式,是通过core(FLC)

到CHA(MLC,LLC),CHA到IMC,IMC到channel,到rank;

详细的内容以后讲,以后讲。CHA的System address decoder,是个独立专题。这个专题,是导致我这一个月停更的大坑。我要好好想想该怎么写。

三、IIO

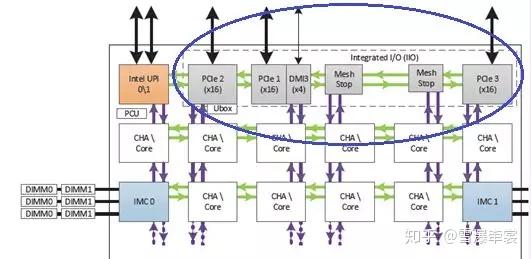

IIO的全称Integrated I/O module,集成IO模组。如下图蓝色椭圆处:

IIO module 其实就是我们之前说的CPU直连PCIE 的四个stack模组。

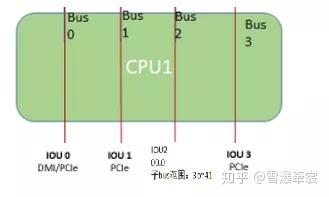

每个SKX CPU的 IIO modules有四个:

DMI3:有时候又称为IOU0。是个PCIE3x4的PCIE STACK。在CPU0中的DMI3通常用于连接 PCH;

PCIE1:有时候又称为IOU1。是个PCIE3x16的PCIE STACK。

PCIE2:有时候又称为IOU2。是个PCIE3x16的PCIE STACK。

PCIE3:有时候又称为IOU3。是个PCIE3x16的PCIE STACK。

PCIE1,2,3,提供给了服务器品牌厂商,服务器品牌厂商根据自己的服务器定位以及客户需求,会对PCIE1,2,3,进行分劈形成一个一个的rootPort(例如,pcie1 从 一个pcie3x16分成 两个pcie3x8或四个pcie3x4)。

——所以,在度娘的很多搜索资料里,所谓“SKylake CPU提供了48个直连PCIE lane”,意思就是PCIE1,2,3加起来总共提供了48条 pcie gen3 lanes。如下图:

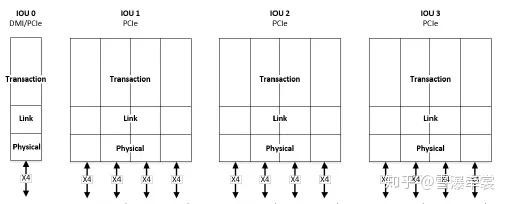

所谓的PCIE stack,是指该iio module 可以根据需要将所包含的16个lane做以下操作:

1、直接形成一个x16的PCIE rootport;(例如用于GPU)

或者

2、分劈成两个x8的PCIE rootport;(例如万兆网卡);

或者

3、分劈成四个x4 PCIE rootport;(例如用于NVME);

或者

4、分劈成三个PCIE rootport: x8,x4,x4;

这里还是要说一点,在某些海水司研发的ppt资料里解释说PCIE STACK就是PCIE switch。这种说法我认为是不对的。

我认为IIO/PCIE STACK属于pci的root complex的范畴。或者说可以简单的认为是个pcie hub,是将16个lanes进行分劈(intel 用bifurcate这个词)形成一个或多个root port。

而PCIE switch则能够实现PCIE带宽复用。也就例如说:一个x16 的PCIE 通道输入到PCIE switch ,PCIE switch可以分出四个 x16的输出Port。PCIE switch的实际产品例如BRODCOM PEX9797。

然后我觉得有必要对比一下skylake 的前一代和skylake 之间在PCIE总线架构的区别了。

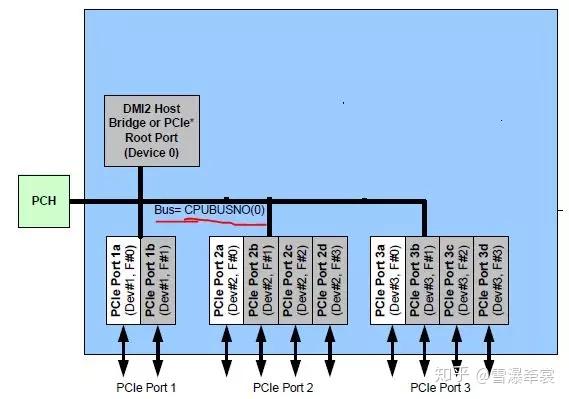

Intel 的前一代v3/v4 CPU(broadwell &haswell),操作系统所能看到的、用于挂载MMIO设备(也是一个DMI和三个 PCIE module)的bus只有一条(其实操作系统还能看到另外一条bus,那条bus只挂载控制类的module),CPU的四个IIO module,都是挂在这同一个PCI BUS0上的,如下图:

而skx 内,操作系统所能看到的、用于挂载 MMIO设备的总线,扩展到了4条。每个IIO module都挂在独立的bus上。如下图:

所以从这二者的对比可以看出:skylake CPU在PCIE寻址方面应该是比上一代Haswell要优化一些的。

以后到SKX CPU PCI BUS总线架构中再详细讲,详细讲。

四、此篇总结

截至目前,CPU的uncore 部件 IMC和IIO已经讲完。标志着我们已将SKX CPU的结构简单的遍历了一遍。就如同我们面对着一个喜马拉雅雪怪,我们现在已经知道这是头,这是胳膊,这是腿,这是尾巴。

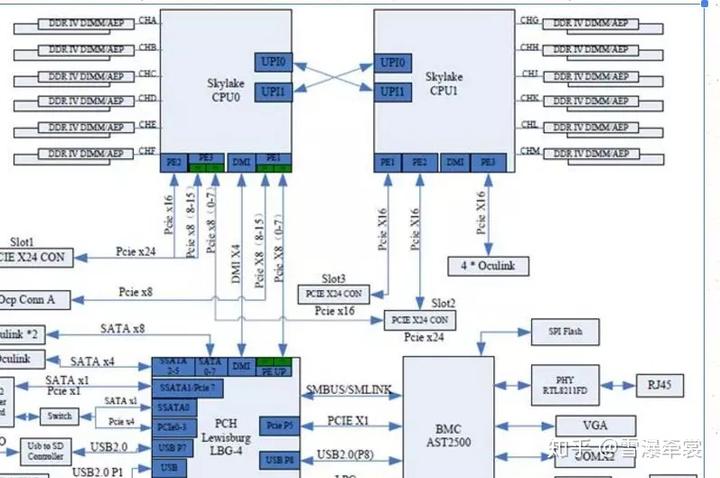

此时,若再有这样的一幅图放在你面前:

我们的眼睛应该会先从CPU开始,对,就是标着skylake CPU的那俩,

=>左右两边,每个CPU各6个内存channel,喔,喔,CPU里有两个IMC,每个IMC各控制3个channel,对的。

=>左右的中间,CPU0和CPU1通过UPI相连,对的。

=>从上往下,CPU0的DMI3连接到了PCH Lewisburg上,喔喔,一堆的SATA,USB等慢速设备接口都是PCH上的lanes转变出来的。

=>再回到CPU0,1,喔喔PCIE1,2,3被劈成了若干个PCIE conn。咦,怎么还有X24的PCIE conn?装B,一定是装B,不可能是一个pcie槽,一定是x16+x8伪装的……

=>当然右下角还有个BMC,那是我们实现服务器可服务性的最重要的管理接口(ipmi)。

——啊,从今天起,我们将不再是陌生人。

其实CPU的uncore部件里,还有一个UPI没有讲。UPI涉及socket与socket的互联。如果我们不涉及2路,4路,8路CPU的互联拓扑,UPI就几乎涉及不到了。所以UPI不讲了。

服务器的架构,终究是以实现功能逻辑为目的的。现代的CPU socket更是整个服务器架构的核心功能部件组,牢牢把握着功能逻辑的控制权。

当然服务器架构中还有几个具有“相对独立”的诸侯,例如BMC,raid card,GPU 加速card,FPGA等。这几个领域又在CPU+chipset 的大王国里,形成了依附的小诸侯国。

但不可否认,intel CPU+chipset是X86服务器架构的基础。所以本系列接下来将分析skylake CPU的ras功能实现以及某些服务器产品的内存编址和pci架构,一窥intel x86服务器架构。

按照intel xeon的习惯,一代平台搭载两代CPU,例如grantley平台搭载v3和v4 CPU。而这两代CPU,架构基本相同。intel这种玩法,被人诟病为“挤牙膏”。同样我讲的skylake和目前刚开始量产的cascadelake服务器,估计也是这种玩法。真正架构要发生变化的,要等whiteley平台+Cooperlake/icelake了。

以下两类“流”,是我用最简单的语言来概括我对的skylakeCPU架构功能的理解,不一定严谨:

Skylake CPU的状态控制流:

1、Core <=>UBOX<=>uncore各个组件;

2、Core <=>PCU<=>外部;

Skylake CPU的数据流:

1、Cache 缺页:Core <=>cache <=>mem(imc);

2、DCA:Core <=> cache<=>PCIE;

3、DMA: mem(imc)<=>PCIE;

后面,我们将以功能的角度,展现功能所需要的寄存器,以及寄存器的数据结构。力图最终展现出intel X86架构的逻辑。

目前能想到的专题是:

1、 intel 严重错误MCE and IERR处理架构。

2、 PCI基础知识和SKX CPU PCI BUS总线架构。

3、 PCIE 错误处理机制

4、 CHA DRAM寻址机制。

5、 CHA MMIO&MMCFG寻址机制。

6、 UEFI 引导、PCIBUS编址和APEI初始化

7、 X86服务器硬件可维护性架构。

8、 X86服务器日志分析实战。

9、 海水司服务器NF5280M5可维护性缺陷分析。

——呃,当这些专题逐一罗列出来后才发现,我还真是售后出身的不入流啊……

用一则现代寓言作为本片结尾。

文化苦旅

十年前的北京,扫黄时,抓了一个小姐。

检查小姐姐的包——除却那类物品,赫然一本《文化苦旅》。

警察蜀黍觉得奇怪:一个小姐,随身揣本书干啥。

小姐回答:现如今客人的品味越来越高,只有随时随地学习,不断加强自身文化修养,才能为客人提供全方位高层次的精神体验。

十年后的济南,又有一个小姐,接客休息的当口,看了同一本书,结果被妈妈桑臭骂不务正业。

发布于 2020-06-03 17:22

「真诚赞赏,手留余香」

还没有人赞赏,快来当第一个赞赏的人吧!

x86

服务器架构

英特尔 (Intel)