1:历史性突破Xilinx A7、K7、V7、ZYNQ、KU等FPGA芯片的LabVIEW在线前面板交互式运行

副标题:重大更新1:利用Xilinx JTAG下载器自动下载6系列7系列(Spartan6、Artix7、Kintex7、Virtex7、ZYNQ)LabVIEW FPGA程序(支持在线前面板交互式运行和调试)

我们始终在想一个问题:就是这几十年市面上已有的海量的FPGA芯片、板子、板卡,起码也有几千万个了,如何在不破坏板子、不飞线的情况下,还能以零成本的方式实现LabVIEW FPGA在线前面板交互式运行和上位机FPGA引用读写访问控件的功能?我们做到了!

1、重大突破:历时半年,终于突破了Xilinx 7系列(Artix7、Kintex7、Virtex7)、U系列(KU、KU+、VU、VU+)以及ZYNQ等家族FPGA芯片的LabVIEW在线前面板交互式运行和调试;当然,还有以前就支持的Virtex5/Spartan3E/Spartan6等传统的5系列、6系列FPGA芯片。

2、重大更新:我们是真正对市面上已有的、海量的、任何厂家的Xilinx FPGA板子或板卡,在不做任何改动,不做任何飞线、不破坏板子的情况下,借助大家所熟知的0成本的Xilinx JTAG下载器或者我们研发的SDMC FPGA Downloader以太网下载器,实现了真正意义上的FPGA VI在线前面板交互式运行和调试功能,这是我们与其他封闭式友商最大的不同!

3、重要理念:我们的LabVIEW My FPGA图形化软件工具包和RIO开发方案具有普适性,只有这样,才能让广大用户自由选择市面上已有的、海量的FPGA芯片、板子、板卡或者用户自己自由设计硬件,而不是被其他友商固定的硬件而绑架了。

4、始终秉持:“为所有想用又不敢用、正在使用和将要使用FPGA的广大用户,提供一套通用的国产化、图形化、开源化RIO解决方案”;让所有FPGA芯片、板子、板卡都能享受到图形化编程的乐趣,真正摆脱友商限制,让用户的FPGA产品低成本量产成为可能性,并且牢牢抓住FPGA的灵魂程序!

正文摘录:

经过半年时间的攻关,我们终于可以像开发Spartan6家族芯片那样来开发Xilinx 7系列(Artix7、Kintex7、Virtex7、KU)FPGA和ZYNQ家族芯片了,借助大家平时常用的Xilinx JTAG下载器来完成这个在线前面板交互式运行和调试功能!这是本宝典最大的创新点之一!下面听我慢慢道来!

5.5.1:LabVIEW FPGA开发环境准备工作

熟悉我们Pro1开发宝典的用户知道,要想通过Xilinx JTAG下载器对早期的Xilinx 5系列和6系列FPGA进行在线前面板交互式运行调试的话,需要安装4号文件(ISE 14.7编译器)和6号驱动包(DEFB),因为ISE编译器里面含有IMPACT.exe下载工具,DEFB里面含有NICobs工具链dll;所以,如果想要对Xilinx 7系列(Artix7、Kintex7、Virtex7)和ZYNQ系列FPGA进行在线下载和在线前面板交互式运行调试的话,我们也需要借助这个IMPACT和NICobs来实现!

所以,前面第3章的软件安装部分,我们更新了宝典,强调了要把云盘里面的安装软件文件夹里面的4号ISE 14.7编译器和6号DEFB驱动包一并安装上。安装过程中有一些注意事项,不记得的用户可以回看一下宝典第3章相关内容。

注意1:目前高版本里面只有LabVIEW 2017、2018版本对应的ISE 14.7编译器默认是不支持Win10系统的,而LabVIEW 2015、2019、2020对应的ISE编译器则不限制系统安装;Win7、Win10和Win11都能安装并且无缝兼容,所以平时我们自己用的比较多的版本是2015和2019版本。

注意2:LabVIEW 2015之所以没有系统限制,是因为那个时候Win10还没有起来,NI忘记在安装向导里面加限制了;LabVIEW 2019和2020可以,是因为NI换了一种安装方式,那就是通过NI Package Manager在线或者离线来安装,所以支持安装到Win7、Win10或者Win11里面去。下面的3幅截图就是Win11系统下的LabVIEW 2019对应的ISE 14.7编译器安装截图。尽管在NI Package Manager页面里面显示不支持,但是依然可以执行“下一步”安装,但是唯独2017和2018版本对应的ISE编译器,NI直接把“下一步”按钮给禁用了,那就只能望洋兴叹了!

结论:推荐客户使用LabVIEW 2011、2015、2019、2020这4个版本;LabVIEW 2017、2018不推荐!

提醒:如果有些用户买的是正版的LabVIEW 2017或者2018,同时又找不到Win7系统的电脑,又不愿意换成其他版本的LabVIEW(譬如2015、2019、2020)或者安装Win7虚拟机的话。为了解决这一痛点,我们专门研发了一款以太网下载器,取名为“SDMC FPGA Downloader”,可以直接通过网络的方式将FPGA VI编译下载到FPGA芯片里面运行然后自动进入在线前面板交互式运行模式,并且还支持上位机通过引用的方式来操作下位机FPGA VI前面板上的控件读写,跟NI的板卡完全一样的使用效果!这样,用户就不需要安装IMPACT和DEFB了,也就摆脱了2017、2018与系统兼容性方面的困扰了。实测我们这款以太网下载器SDMC FPGA Downloader,支持Spartan6、Artix7、Kintex7、Virtex7、Kintex UltraScale、ZYNQ等系列FPGA芯片,非常强大,具体的实战演示可以参考宝典后面的第五章的5.7节内容!

接下来,需要运行一下本书配套云盘里面的“Xilinx全系列FPGA LabVIEW在线前面板激活程序.vi”这个程序,如图5-87所示。

双击运行这个激活VI,在弹出来的页面里面,点击左上角的运行箭头,等待15s左右,如果右侧指示灯点亮,说明当前环境下的7系列FPGA在线前面板交互式运行功能激活成功,如图5-88所示。需要这个程序的用户请联系我们(邮箱:DLW30@126.com;微信:myview30)

5.5.2:LabVIEW FPGA VI程序验证平台

为了验证我们这套基于Xilinx JTAG下载器实现LabVIEW FPGA在线前面板交互式运行调试的效果,我们准备了3个厂家,4款不同的7系列FPGA开发板来测试验证。

分别是:

1黑金AX7103开发板(主芯片Artix7-100T);

2黑金AX7A200开发板(主芯片Artix7-200T);

3正点原子达芬奇Pro开发板(主芯片Artix7-100T);

4米联客MA7K325开发板(主芯片Kintex7-325T);

以上4款FPGA开发板对应的实物图,分别如图5-89~5-92所示。另外,我们平时还经常用到黑金的一款K7-325T开发板AX7K325,由于手头没有这个板子,有这块板子的用户,在学完本节内容之后可以自己尝试验证一下在线前面板交互式运行调试功能。

关于这些厂家的FPGA板子介绍,前面第4章里面做过详细的讲解。当然,大家也可以在各个厂家官网或者淘宝上找到更多信息,这些板子也是目前市面上存量最多的板子,性价比高,资料丰富,原理图和元器件库都是开源的,方便用户学会之后自己二次开发,相比于国外的FPGA板子,国内的厂家更加人性化!

另外,关于6系列FPGA芯片的LabVIEW在线前面板交互式运行,原先我们就支持在线下载和前面板运行,感兴趣的用户可以参考Pro1开发宝典,本书重点讲解的是7系列和ZYNQ系列,所以本节就不单独列出了!

注意:由于黑金的ZYNQ开发板上集成的是Digilent HS1/2/3系列下载器,并且没有将JTGA口预留出来,所以也就无法接入Xilinx JTAG下载器了,但是可以通过我们研发的SDMC FPGA Downloader以太网下载器来实现在线前面板交互式运行和调试。

这个我们会在后面的5.6节里面给用户演示。当然了,如果用户的ZYNQ板子上有JTAG下载口,那么可以用本节的方法也就是Xilinx JTAG下载器实现在线前面板交互式运行调试。

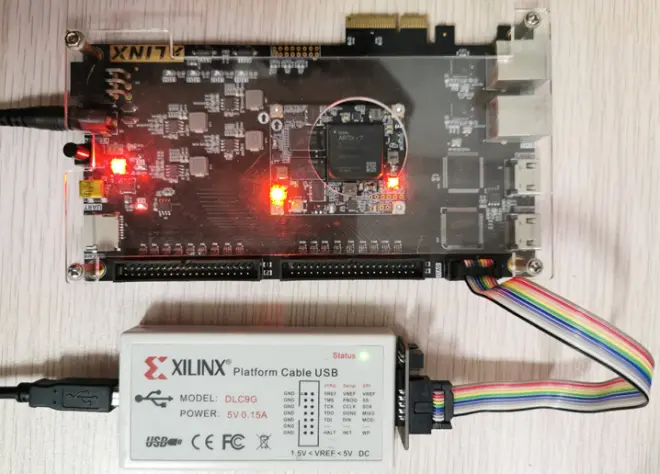

大家平时常用的Xilinx JTAG下载器,如图5-93所示,里面包含了各种不同封装尺寸接口的JTAG线缆,可以兼容目前市面上所有厂家FPGA开发板上的JTAG接口。这里再次提醒一下大家,千万别买错了下载器,一定要选择Xilinx方案的下载器,而不是Digilent HS系列下载器。如果用户不清楚怎么购买Xilinx JTAG下载器,可以联系我们神电测控(邮箱:DLW30@126.com;微信:myview30)。另外,Xilinx下载器的驱动安装相对麻烦一些,建议大家参考我们宝典里面的cmd命令方式来安装这个下载器的驱动比较好(宝典里面搜索cmd关键字进快速定位)。

5.5.3:LabVIEW FPGA VI程序编写与编译

为了验证7系列(Artix7、Kintex7、Virtex7)FPGA VI的LabVIEW前面板在线运行和调试功能,我们重新编写一个FPGA VI程序,通过控制第三方FPGA开发板上的LED灯闪烁频率以及实时捕捉开发板上的按键状态,来展示LabVIEW FPGA在线前面板的强大之处。我们可以通过修改前面板的写入控件数值来实时动态的改变FPGA芯片里面的程序运行周期,并且将按键状态实时呈现在FPGA VI前面板上,而不需要单独再去编写上位机VI来跟下位机通信。

这种下位机FPGA VI在线前面板交互式运行和调试功能的好处就是,不需要反复编译下位机FPGA VI了,避免了时间的浪费,这就是LabVIEW FPGA在线前面板交互式运行和调试的优势之处。

5.5.3.1:新建LabVIEW项目浏览器

点击LabVIEW左上角的“文件”à“新建(N)”à“项目”,新建一个空白的LabVIEW项目浏览器,保存一下,命名为“LabVIEW 7 Serials FPGA Project-Xilinx JTAG.lvprog”,如图5-94所示。

5.5.3.2:新建FPGA终端设备

在刚刚新建出来的项目浏览器里面,右击“我的电脑”,选择“新建”à“终端和设备”,如图5-95所示;然后在弹出来的终端设备列表里面,找到上面3个厂家4款开发板对应的FPGA终端名称,如图5-96(abcd)所示。

选中之后双击或者点击“确定”按钮,即可将这4个FPGA开发板对应的FPGA终端添加到项目里面来,如图5-97所示。

展开之后,可以看出每个厂家的系统板载晶振特点:黑金喜欢在7系列FPGA板子上,将板载晶振弄成200MHz差分时钟;正点原子喜欢用更低的50MHz单端时钟板载晶振;米联客则在二者之间取了一个中间值,比如100MHz单端时钟。

实际上,FPGA系统默认的Onboard时钟晶振频率太高和太低都不太好,太高会导致LabVIEW里面的普通while循环编译出现定时错误,太低的话,很多线程需要通过PLL或者MMCM进行倍频才能通过提高速度减少资源的消耗。

因此,我们建议,用户在设计自己的FPGA板卡时,尽量选择一个中间档位的板载时钟频率,比如50MHz或者100MHz。对NI比较熟悉的用户知道,NI更喜欢用40MHz晶振作为系统时钟。

为了更加形象生动的展示FPGA VI前面板的在线实时运行和调试功能,我们可以右击FPGA终端设备名称,选择添加“FPGA I/O”,然后将LED指示灯和KEY按键对应的FPGA引脚资源EIO节点添加到FPGA里面来,如图5-98所示。

5.5.3.3:编写FPGA VI程序

接下来,我们可以通过编写一个简单的FPGA VI程序来验证我们的LabVIEW My FPGA在线前面板交互式运行和调试功能可以在7系列FPGA上完美的呈现出来。

这个FPGA VI程序的具体编写过程,这里就不在详细展开了,因为程序框图比较简单,我们直接给出4个FPGA开发板终端对应的FPGA VI前面板和程序框图,分别如图5-99~5-102所示。

这4个FPGA VI实现的功能都是相同的,那就是通过while循环实时捕捉FPGA开发板上的按键状态,并在前面板上通过布尔指示灯显示出来;另外一个功能通过程序周期性取反来控制FPGA板子上的LED指示灯进行闪烁,闪烁频率则由前面板上的输入控件“控制循环周期(mSec)”里面的数值来决定;最后整个while循环的运行次数,也就是i值通过显示控件“Running”和“仪表”显示在前面板上。

传统的VHDL和Verilog是没有办法实现UI界面的,所以每次修改一个参数都需要重新花费大量的时间进行编译;而我们的LabVIEW FPGA天生就有一个前面板可以充当UI调试界面,这个与生俱来的功能就是本书重点强调的LabVIEW FPGA在线前面板交互式运行、仿真、调试。

5.5.3.4:编译FPGA VI程序

FPGA VI程序编写完成后,接下来就是编译了,用户只需要点击一下FPGA VI前面板左上角的运行箭头,即可弹出编译提示对话框,首次弹出会自动创建一个程序生成规范,用户需要在程序生成规范里面勾选“加载至FPGA时运行”,不然后续在将FPGA bit文件固化到Flash芯片里面,FPGA加载后不会执行的。因此,我们提前将这一步做掉,即在程序生成规范里面勾选“加载至FPGA时运行”,如图5-103所示。

当我们点击FPGA VI运行箭头,会弹出编译器选择对话框,如图5-104所示,选择默认的第一项“使用本地编译服务器”,因为我们在前面第3章的时候已经将NI裁剪过的Vivado编译器安装到本地计算机上了!当然也可以选择网络服务器或者NI云编译,关于这两项的讲解,请参考前面5.3节相关内容,这里不再赘述!

点击“确定”按钮后,LabVIEW会自动将FPGA VI程序框图转换成VHDL代码,如图5-105所示。

经过综合、布局布线、时间约束等步骤后,如果一切顺利,大概两三分钟后,LabVIEW FPGA编译状态窗口会提示编译完成,如图5-106,通过这个编译状态窗口可以看到当前消耗的FPGA资源情况。提醒:本节编译很顺利,跟前面5.3节里面报错完全不同,因为我们已经突破了7系列FPGA的编译、下载和在线前面板交互式运行和调试功能。

当上面编译完成后,会弹出一个“正在准备交互式执行”对话框,如图5-107所示,这个想必用过NI或者看过我们Pro1的客户很熟悉,正是LabVIEW FPGA启动在线前面板交互式运行调试功能的提示框;如果大家还没有将Xilinx JTAG下载器和FPGA开发板接到这台电脑或者接的不是Xilinx JTAG下载器而是Digilent HS系列下载器,等一会会弹出一个超时错误对话框,提醒用户找不到下载通信线缆,也就是说主机找不到Xilinx JTAG下载器,如图5-108所示。

重大更新:很多用户关心的是Vivado编译器编译出来的原始bit文件,而不是NI的lvbitx文件,因为原始的FPGA bit文件更灵活更方便,将这个原始的bit文件发给任何人都可以通过任何手段下载到FPGA里面运行;虽然上面我们没有连接下载器和FPGA板子到电脑上导致下载超时,但是LabVIEW项目浏览器所在路径下的“FPGA Bitfiles”文件夹里面依然会自动生成一个同名的原始bit文件,如图5-109所示。

这个自动生成原始FPGA bit文件的功能是我们在后台帮大家实现的,也就是说,用户再也不需要像前面5.3节那样总是开着获取bit文件的程序才能得到原始bit文件。很明显经过我们重大更新后的宝典和My FPGA工具包更方便更易用,体验效果跟NI完全一样!

5.5.4:FPGA开发板+Xilinx JTAG下载器连接实物图

接下来,将Xilinx JTAG下载器接到黑金、米联客、正点原子的4款FPGA开发板上面,另外一头接到开发电脑上,如图5-110~5-113所示。

注意1:由于每个厂家的FPGA开发板预留的JTAG座子封装尺寸都不一样,好在国人做的Xilinx JTAG下载器配套了很多种转接线,可以完全兼容市面上所有的FPGA硬件,真正做到以不变应万变!

注意2:再次强调一下,Xilinx JTAG下载器的驱动安装方法,推荐使用cmd命令方式来安装,尤其是需要管理员权限和数字签名的系统,这种方法最好;用户可以在宝典里面搜索关键字“cmd”,快速定位到安装那一节内容。

下载器驱动安装好之后,可以在设备管理器里面找到,如图5-114所示。

5.5.5:LabVIEW FPGA在线前面板交互式运行(基于传统的Xilinx JTAG下载器)

接下来,就是见证奇迹的时刻了,大家屏住呼吸哈

硬件接好之后,给FPGA开发板上电,然后再点击一下编译过的FPGA VI前面板左上角的运行箭头,可以看到几秒之后,奇迹发生了,下位机FPGA VI前面板竟然活了,就像我们开发的LabVIEW STM32工具包那样,LabVIEW前面板成功地进入了FPGA在线交互式运行模式,并且下位机FPGA VI前面板上的“Running”和“仪表”,这两个显示控件里面的数值会按照500ms的速度进行+1递增,如图5-115~5-118所示。

同时可以看到,4款FPGA开发板上的LED指示灯按照1Hz的频率一齐同步闪烁,亮灭持续时间各500ms,如图5-119~5-122所示。

如果我们在FPGA VI交互式前面板上修改一下“控制循环周期(mSec)”控件里面的数值,比如改成100,如图5-123(abcd)所示,此时FPGA开发板上的LED闪烁频率明显加快了,并且仪表盘的指针也开始加速移动!

接着,我们尝试按压FPGA开发板上的按键KEY,发现FPGA VI前面板上相对应的布尔指示灯也跟着发生变化,如图5-124(abcd)所示。这就是进入在线交互式运行前面板之后的LabVIEW FPGA强大之处,通过读写FPGA内部的寄存器将FPGA前面板上的所有控件信息自动投射关联并实时显示到当前FPGA VI前面板上。

说明下位机FPGA实时捕捉到的状态通过在线交互式运行模式自动呈现在了FPGA VI前面板上了,非常直观!妈妈再也不用担心反复编译、再也无须借助串口打印来调试了!

5.5.6:LabVIEW FPGA程序固化到Flash(基于传统的Xilinx JTAG下载器)

当我们借助LabVIEW FPGA强大的在线交互式运行前面板调试完FPGA VI程序后,就可以将这个FPGA VI进行批量部署了,也就是把编译出来的FPGA原始bit文件转成mcs或者bin文件固化到FPGA开发板上的Flash芯片里面。

前面5.4节我们向大家介绍了可以通过Vivado手动将FPGA bit文件固化到Flash芯片里面,但是那个方法过于复杂,操作起来非常不方便!感兴趣的用户可以自行了解一下即可,无须深入学习5.4节,除非是一种特殊的情况,那就是你设计的FPGA产品卖给了你的用户,当你的FPGA bit文件升级了,你把最新的bit文件发给远在其他城市的客户,需要将这个bit文件重新固化到你的FPGA板子里面去,但是你的客户又不懂LabVIEW,此时,你可以教他如何利用Vivado进行手动下载和固化。

5.5.6.1:LabVIEW FPGA VI Flash固化简介

为了让我们的LabVIEW My FPGA工具包,跟NI FPGA硬件开发有着相同的用户体验,我们将整个FPGA bit文件到mcs/bin文件格式的转换、下载器速度的设置以及各种Flash芯片的选择,全部在后台自动完成,极大的方便了用户的使用!

具体操作方法非常简单,跟Pro1开发宝典里面操作6系列FPGA一样。用户只需要右击编译好的FPGA VI名称,在弹出的菜单中选择“Download Bit to Flash”这个选项,如图5-125所示,就可以将7系列(Artix7、Kintex7、Virtex7、ZYNQ)FPGA bit文件自动固化到FPGA板子上的Flash里面。

点击之后,会弹出一个Flash芯片型号选择页面,这个对话框页面是我们专门为了方便用户开发的,如图5-126所示。我们已经将目前所有已知的Flash芯片型号、容量大小、以及SPI/BPI读写数据位宽等,全部封装到下拉列表里面,用户无须记忆任何TCL指令,只要查看一下FPGA硬件原理图上的Flash芯片型号即可,然后在下拉列表里面选择即可。

但是需要注意的是:很多厂家做的FPGA板子为了降低硬件成本,实际焊接的Flash芯片跟其提供的说明书有时候对不上,导致固化总是不成功,此时,保险起见,最好用眼睛实际观察一下FPGA板子上Flash芯片的具体型号和厂家,这种情况时有发生!经验之谈、少走弯路!

下面我们还是先简单介绍一下这个软件的功能和注意事项,然后再结合黑金、米联客、正点原子等几家FPGA开发板上的Flash芯片型号来实际测试一下固化效果。

首先是Flash存储芯片的类型,我们将其分成3类,如图5-127所示。分别是第三方SPI接口的Flash芯片、Xilinx官方的PROM芯片、第三方BPI接口的Flash芯片。其中,SPI接口的Flash因为厂家众多,性价比高而被广大FPGA厂商所采用;Xilinx官方的PROM兼容性最好,读写速度快,一般用于高端产品里面;BPI接口的Flash基本上很少见。

使用过很多FPGA板子的用户知道,目前国内的FPGA厂家基本上选择的都是SPI接口的Flash作为存放FPGA bit文件的存储芯片。

当选择好Flash芯片类型之后,比如,最为常见的SPI接口Flash芯片;然后下方的Flash下拉列表里面就会自动出现各种不同封装和不同容量大小的Flash型号,如图5-128所示。其中,SPI接口的Flash种类大致可以划分为W25Q系列、N25Q系列、S25FL系列、AT45DB系列等等;关于BPI接口和Xilinx官方的PROM型号,感兴趣的用户可以在我们这个软件里面浏览一下便知,这里不再赘述!

需要注意的是,位于Flash芯片型号右侧的“Flash_Size(MBytes)”是指当前选择的Flash芯片容量大小,单位是M字节,不是小bit,而Flash芯片型号名称里面的数字往往表示的容量单位却是M小bit。

举例说明,比如我们选择了N25Q256这款芯片,那么右侧的容量需要填写32MB,因为N25Q256字符里面的256是小Mbit,需要除以8,才是大写的Mbyte;另外,这个Flash容量大小,需要用户自己手动输入,切记不要填错了!

最后需要注意的是:FPGA终端模板对应的xdc约束文件里面定义的Flash SPI读写数据位宽是×几模式的,比如正点原子达芬奇Pro板子里面我们设置的SPI位宽是X4,如图5-129所示;那么就需要在固化页面的“Flash SPI/BPI Datawidth”下拉列表里面选择SPIx4 mode,保持一致,如图5-130所示,否则固化会失败!如果xdc约束文件里面没有定义SPI读写数据位宽的话,那么下拉列表里面选择默认的SPIx1模式来固化即可。

全部选择好之后,点击“Download”下载按钮,等待一会就会提示下载成功,具体时间要看选择的Flash芯片质量了;固化成功后,如果弹出的提示框里面提醒用户虽然固化了bit文件,但是重新上电FPGA程序并没有运行的话,那就需要检查一下,看看程序生成规范里面是不是忘记了勾选“加载至FPGA时运行”;如果没有勾选,需要重新勾选一下这个“加载至FPGA时运行”,然后重新编译一下FPGA VI,最后再做一次固化流程就可以了,如图5-131.

为了验证固化到Flash里面的FPGA bit程序功能是否正常,可以将FPGA硬件重新上电或者按下FPGA开发板上的Prog编程键测试一下。

注意:固化Flash的过程,是不限制下载器类型的,Xilinx JTAG和Digilent HS系列下载器均可以。

接下来,进入实战环节,将前面编译好的FPGA VI通过右击的方式固化到黑金、米联客、正点原子这4款FPGA开发板的Flash里面去。

5.5.6.2:LabVIEW FPGA VI固化到黑金FPGA开发板的Flash芯片里面

首先根据黑金、米联客、正点原子提供的FPGA开发板原理图找到上面的Flash芯片具体型号,比如黑金的AX7103和AX7A200开发板上的Flash芯片都是N25Q128,如图5-132所示。可以看出,这款Flash容量是128Mbit,换成大B就是16MByte。

然后找到黑金FPGA开发板AX7103和AX7A200对应的终端模板文件所在的路径,如图5-133和5-134所示。到这个文件夹里面找到xdc约束文件,为了区分,我们特地在AX7103开发板对应的xdc没有添加SPI位宽定义,相当于默认的x1模式;而AX7A200开发板对应的xdc约束里面我们加了set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]这句话,如图5-135所示,那就意味着FPGA VI编译生成的bit文件内部将读写位宽设置的是x4模式,也就是当FPGA上电从Flash里面可以通过SPI x4模式并行读取,提高了bit文件加载和启动速度。

所以,通常情况下,只要FPGA板子上的Flash芯片引脚支持x4的话,建议大家在xdc约束文件加上set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]这句话,这样后续FPGA程序加载启动速度更快,体验更好!

知道了上面的信息,我们就可以在LabVIEW FPGA VI固化页面的下拉列表里面选择对应的类型即可。

1)针对黑金AX7103 FPGA开发板,可以右击该终端下编译过的FPGA VI名称,选择菜单里面的“Download Bit to Flash”,如图5-136所示。然后在弹出来的页面里面,Flash芯片型号选择N25Q128;容量设置为16MByte;SPI数据读写位宽选择x1模式,如图5-137所示。

2)针对黑金AX7A200 FPGA开发板,同样右击该终端下的FPGA VI名称,选择菜单里面的“Download Bit to Flash”,然后在弹出来的页面里面,Flash芯片型号选择N25Q128;容量设置为16MByte;SPI数据读写位宽选择x4模式,如图5-138所示。

3)最后,点击页面“Download”下载按钮,出现一个bit文件下载进度条,大约等待几十秒,会弹出Flash烧写成功提示框,如图5-139所示。然后将黑金FPGA开发板断电再上电,就能看到先前我们编写的FPGA VI程序成功的被加载和运行了。

5.5.6.3:LabVIEW FPGA VI固化到正点原子FPGA开发板的Flash芯片里面

正点原子达芬奇Pro开发板(Artix7-100T)上的Flash芯片也是N25Q128,如图5-132所示。这款Flash芯片容量是128Mbit,换成大B就是16MByte。

然后找到正点原子达芬奇Pro FPGA开发板对应的终端模板文件所在的路径,如图5-141所示。到这个文件夹里面找到xdc约束文件,双击打开这个xdc文件,可以看到正点原子达芬奇Pro A7-100T开发板对应的xdc约束文件里面也有这句话:set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design],如图5-142所示,意味着FPGA VI编译生成的bit文件内部读写位宽是x4模式,当FPGA上电从Flash里面可以通过SPIx4模式以4bit并行读取,提高了加载启动速度。

再次提醒:只要FPGA板子上的Flash芯片引脚支持x4的话,建议用户在xdc约束文件加上set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]这句话,这样FPGA重新上电之后的程序加载会更快!

根据以上信息,直接在LabVIEW FPGA VI固化页面的下拉列表里面选择对应的Flash器件型号和容量即可。

针对正点原子达芬奇Pro FPGA开发板,可以右击该终端下编译过的FPGA VI名称,选择菜单里面的“Download Bit to Flash”,如图5-143所示。然后在弹出来的页面里面,Flash芯片型号选择N25Q128;容量设置为16MByte;SPI数据读写位宽选择x4模式,如图5-144所示。可以看出,正点原子的达芬奇Pro跟黑金的A7板子配置基本一样。

然后,点击“Download”下载按钮,会出现一个进度条,大约等待几十秒,弹出Flash烧写成功提示框,如图5-145所示。最后,将正点原子FPGA开发板断电再上电,就能看到先前编写的FPGA VI程序成功地被加载和运行了。

5.5.6.4:LabVIEW FPGA VI固化到米联客FPGA开发板的Flash芯片里面

米联客MA7K325开发板(Kintex-325T)上的Flash芯片是S25FL256,如图5-146所示。这款Flash芯片容量是256Mbit,换成大B就是32MByte。

注意:米联客,有些批次的K7开发板上用的Flash芯片换成了W25Q256或者N25Q256,但是原理图上没有改,所以大家一定要用肉眼观察一下FPGA开发板或者核心板上的Flash具体厂家和型号。

然后找到米联客MA7K325 FPGA开发板对应的终端模板文件所在的路径,如图5-147所示。到这个文件夹里面找到xdc约束文件,双击打开这个xdc文件,可以看到米联客MA7K325开发板对应的xdc约束文件里面同样也有这句话:set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design],如图5-148所示,意味着FPGA VI编译生成的bit文件内部读写位宽是x4模式,当FPGA上电从Flash里面可以通过SPIx4模式以4bit高速并行读取,提高了bit文件的加载速度。

提醒:只要FPGA板子上的Flash芯片接线支持x4的话,建议大家在xdc约束文件加上set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]这句话,这样FPGA重新上电之后的程序加载会更快!

根据以上信息,直接在LabVIEW FPGA VI固化页面的下拉列表里面选择对应的Flash型号和容量即可。

针对米联客MA7K325 FPGA开发板,可以右击该终端下编译过的FPGA VI名称,选择菜单里面的“Download Bit to Flash”,如图5-149所示。然后在弹出来的页面里面,Flash芯片型号选择S25FL256S;容量设置为32MByte;SPI数据读写位宽选择x4模式,如图5-150所示。可以看出,米联客选择的Flash跟黑金和原子不是一个厂家的,因为编译出来的Kintex7 FPGA bit文件要比Artix7大一些,所以用来存放bit文件的Flash容量也要大一些。

然后,点击“下载”按钮,会出现一个进度条,大约等待几十秒,弹出Flash烧写成功提示框,如图5-151所示。最后,将正点原子FPGA开发板断电再上电,就能看到先前编写的FPGA VI程序成功地被加载和运行了。

结论:通过4个板子上电从Flash里面加载bit文件的速度可以看出,SPI x4秒杀SPI x1,因此,建议用户在设计自己的FPGA板子时,尽量选择支持SPI x4模式的Flash芯片。