硬件电路设计-关于串口的数据构成和测试

串口波特率和信号时钟频率的关系

关于串口数据的形式,如果没有做过数字设计,估计很少有人去了解它的数据波形,或者说即使了解过也忘得差不多了。因为实际工程中,几乎不会去测试串口波形,无论是用哪种技术方案,只要带串口的,一般都有现成稳定的驱动,所以能遇到问题去测试的机会少之又少。

在工程开发中,经常用串口来打印一些信息辅助软硬件调试,最常用的调节变量一般是波特率,像其他的位宽、停止位数、奇偶校验、极性、或者Flow control都很少去调。

很多人容易把波特率跟时钟频率混在一起理解,其实两个是不同的概念,频率就是时钟的频率,但是波特率不一样,波特率表示一个单位时间(1s)内传输的bit数,比如波特率115200bps表示连续传输情况下,在1s时间内传输了115200个bit,在信号线上表现的每个bit所占时间为:

1Hz/115200 ≈ 8.68us

而此时的时钟频率约为115.2073kHz,所以波特率≠信号时钟频率。

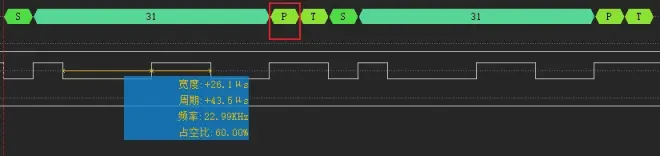

下图是逻辑分析仪抓取串口以波特率115200bps、位宽8bit、无奇偶校验、1bit停止位发送的波形,可以看到,解析测量到的一个bit时间长度是8.7us,跟我们上面计算的一样。

图1. 波特率115200一个bit的时间长度

串口数据波形的解析和测试 看了上面的波形,我们也可以很清晰的知道,串口在没有数据通信时信号线上是高电平,一个bit低电平表示数据的开始,然后传对应位宽的数据,加上奇偶校验,如果没有则不加,然后最后一个bit时间的高电平表示一次的数据传输结束。典型的数据帧构成如下图所示。

图2. 串口的一帧数据构成

为什么要一个bit的时间长度表示数据传输的结束呢,可以看上图图1的第二个数据的开始信号,我们现在也知道了串口由高电平拉低并维持一个bit的低电平时间长度表示数据的开始,如果一个数据结束不是高电平,那第二个数据的开始是无法被识别的,当然,这个停止位的时间宽度,还可以设置为1.5个或2个bit的时间宽度,取决于系统对数据传输的稳定性要求,不过一般一个bit位已经足够。下图为8bit数据的时间长度测量情况,可以看到总时间宽度为69.3us,按照上面的信息计算理论值为69.44us,在误差范围内,所以可以确定为8bit位宽没错。

图3. 波特率115200的8bit位宽时间长度测量

当我尝试把数据宽度改为5bit时,同样发送字符'1',抓取到的波形如下,可以看到,字符'1'的x031的高3bit没了,发送出来的数据为低5bit数据。

图4. 波特率115200、5bit位宽发送0x31的波形

把数据位宽改为6bit时,可以看到0x31能被识别了出来。

图5. 波特率115200、6bit位宽,1bit停止位,发送0x31的波形

把数据位宽改为8bit,2bit停止位。

图6. 波特率115200、8bit位宽,2bit停止位,发送0x31的波形

下面来尝试数据位宽改为8bit,1bit停止位,奇校验。这里先说下串口的奇偶校验。奇偶校验用来确保传输的数据中有奇数个或者偶数个逻辑高电平,即如果设置奇校验输出,如果数据位中有3个bit逻辑1,那么此时满足逻辑1为奇数条件,校验位此时会自动调节为逻辑0。如果数据位中有2个bit逻辑1,那么此时不满足逻辑1为奇数的条件,校验位会自动变为逻辑1来满足数据+校验位组合得到的逻辑1为奇数。

同理,如果设置为偶校验,当数据中的逻辑1为偶数个时,校验位会自动变为逻辑0,确保数据+校验位的组合得到的逻辑1为偶数,如果数据中的逻辑1为奇数,那么校验位会自动变为逻辑1,确保数据+校验位组合得到的逻辑1为偶数,各种情况如下图所示。

图7. 波特率115200、8bit位宽,1bit停止位,奇校验,发送0x31的波形,可以看到校验位此时为 0

图8. 波特率115200、8bit位宽,1bit停止位,奇校验,发送0x30的波形,可以看到校验位此时为 1

图9. 波特率115200、8bit位宽,1bit停止位,偶校验,发送0x31的波形,可以看到校验位此时为 1

图10. 波特率115200、8bit位宽,1bit停止位,偶校验,发送0x30的波形,可以看到校验位此时为 0

* 著作权归公众号ecircuitlab所有。商业转载请联系作者获得授权,非商业转载请注明出处。