4:历史性突破Xilinx A7、K7、V7、ZYNQ、KU等FPGA芯片的LabVIEW在线前面板交互式运行

副标题:重大更新4:上位机直接通过VI/规范/lvbitx等FPGA引用方式来访问下位机FPGA VI前面板上的控件(高级功能,至于超高速的PCIe/PXIe DMA FIFO功能请参考本书第7、8章相关内容)

我们始终在想一个问题:就是这几十年市面上已有的海量的FPGA芯片、板子、板卡,起码也有几千万个了,如何在不破坏板子、不飞线的情况下,还能以零成本的方式实现LabVIEW FPGA在线前面板交互式运行和上位机FPGA引用读写访问控件的功能?我们做到了!

1、重大突破:历时半年,终于突破了Xilinx 7系列(Artix7、Kintex7、Virtex7)、U系列(KU、KU+、VU、VU+)以及ZYNQ等家族FPGA芯片的LabVIEW在线前面板交互式运行和调试;当然,还有以前就支持的Virtex5/Spartan3E/Spartan6等传统的5系列、6系列FPGA芯片。

2、重大更新:我们是真正对市面上已有的、海量的、任何厂家的Xilinx FPGA板子或板卡,在不做任何改动,不做任何飞线、不破坏板子的情况下,借助大家所熟知的0成本的Xilinx JTAG下载器或者我们研发的SDMC FPGA Downloader以太网下载器,实现了真正意义上的FPGA VI在线前面板交互式运行和调试功能,这是我们与其他封闭式友商最大的不同!

3、重要理念:我们的LabVIEW My FPGA图形化软件工具包和RIO开发方案具有普适性,只有这样,才能让广大用户自由选择市面上已有的、海量的FPGA芯片、板子、板卡或者用户自己自由设计硬件,而不是被其他友商固定的硬件而绑架了。

4、始终秉持:“为所有想用又不敢用、正在使用和将要使用FPGA的广大用户,提供一套通用的国产化、图形化、开源化RIO解决方案”;让所有FPGA芯片、板子、板卡都能享受到图形化编程的乐趣,真正摆脱友商限制,让用户的FPGA产品低成本量产成为可能性,并且牢牢抓住FPGA的灵魂程序!

部分摘录:

前面5.5节和5.6节重点向大家展示了如何借助传统的Xilinx JTAG下载器以及我们自研的SDMC FPGA Downloader以太网下载器实现FPGA VI程序的LabVIEW在线前面板交互式运行和调试。

相当于我们只需要通过LabVIEW编写一个下位机FPGA VI,就可以将其下载到FPGA芯片里面运行,同时前面板还活了。这个前面板既是下位机FPGA的UI,又可以看成是一个简易的上位机调试界面;最大的优势是不需要再单独编写一个上位机程序,节约了开发和调试时间;因为单独编写上位机程序来配合下位机FPGA一起调试的话,往往二者之间的通信协议要设计的很完善,不然有可能会带来一些额外的bug,最后可能都不确定是下位机FPGA程序问题还是二者之间的通信协议问题还是数据解析问题。

本节要跟大家介绍的是LabVIEW FPGA工具包的高级功能,就是上位机LabVIEW应用程序可以直接通过调用FPGA VI或者程序生成规范或者编译出来的lvbitx文件,实现对下位机FPGA VI前面板上控件的实时访问和控制。

这样就不需要用户单独去设计上位机跟下位机FPGA之间的通信协议了,而是由LabVIEW FPGA工具包在底层自动完成数据传输和协议解析,相当于一个透明的黑匣子。无论物理上FPGA走的是PCIe/PXIe还是以太网通信,LabVIEW FPGA工具包都可以实现底层屏蔽,用户不需要去了解底层的传输协议,而是上位机直接通过调用 “lvbitx/VI/程序生成规范”就可以将数据拿到以及完成对控件的读写。

这种方式有利有弊,好的地方在于可以简化上位机编程,不需要用户自己设计传输协议;不好的地方在于底层LabVIEW FPGA封装的层次太多,牺牲了一些PCIe/PXIe或者以太网的传输带宽。

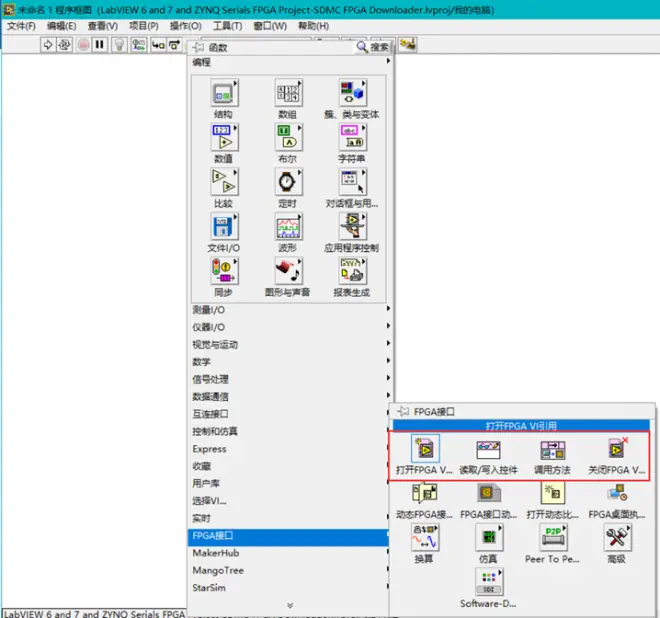

所以,我们在设计LabVIEW My FPGA软件工具包和编写宝典的时候,取其长处,摒除缺点,保留了LabVIEW FPGA在线前面板交互式运行以及上位机通过“lvbitx/VI/程序生成规范”访问下位机FPGA VI前面板上的控件功能。当然,这些功能的实现离不开NI提供的上位机FPGA Interface函数选板里面的VI,如图5-292所示。

而对那些需要实现连续数据流读写的DMA FIFO应用来说,我们单独开发了一套机制,优先保留了PCIe/PXIe总线的高速传输带宽(6.4Gbit/s),这样用户才能基于FPGA实现真正意义上的高速采集。关于这部分内容请参考宝典的第7和第8章。这里不再赘述!

接下来,我们向大家介绍并演示一下上位机LabVIEW程序是如何通过打开“FPGA VI或者FPGA程序生成规范或者lvbitx文件”引用的方式实现对下位机FPGA前面板上的控件读写。

为了验证基于传统的Xilinx JTAG下载器和基于我们自研的SDMC FPGA Downloader以太网下载器,二者都可以实现上位机LabVIEW通过“FPGA VI引用”的方式访问下位机FPGA前面板上的控件,下面分成两个实验给大家展示一下过程。

5.7.1:基于传统的Xilinx JTAG下载器实现上位机FPGA引用的方式访问下位机FPGA VI

5.7.1.1:实验平台:Xilinx JTAG下载器+黑金AX7103 FPGA开发板(Artix7-100T)

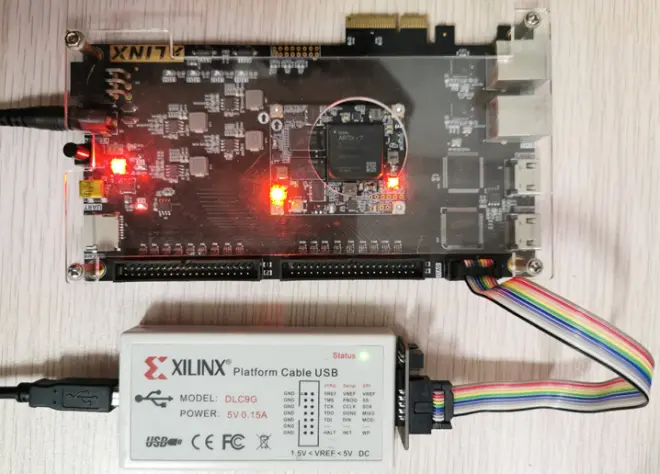

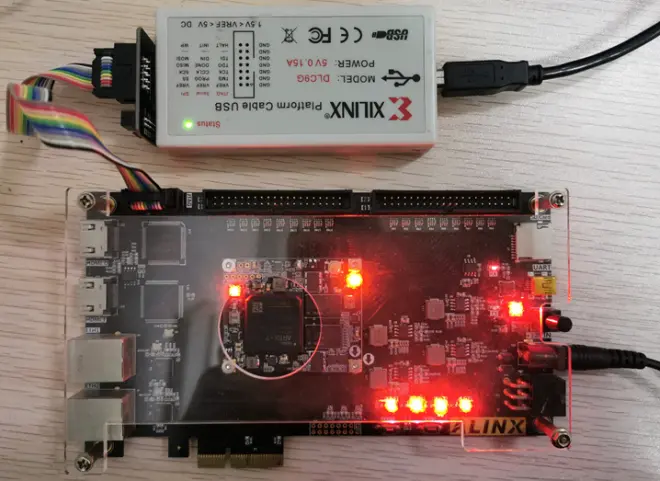

为了验证基于Xilinx JTAG下载器也能通过上位机LabVIEW以FPGA VI引用的方式来控制和访问下位机FPGA程序,我们选取本书配套的黑金AX7103 FPGA开发板来做测试,图5-293显示的是AX7103 FPGA开发板与Xilinx JTAG下载器互联实物图。

5.7.1.2:上位机LabVIEW程序编写(调用FPGA VI引用方式)

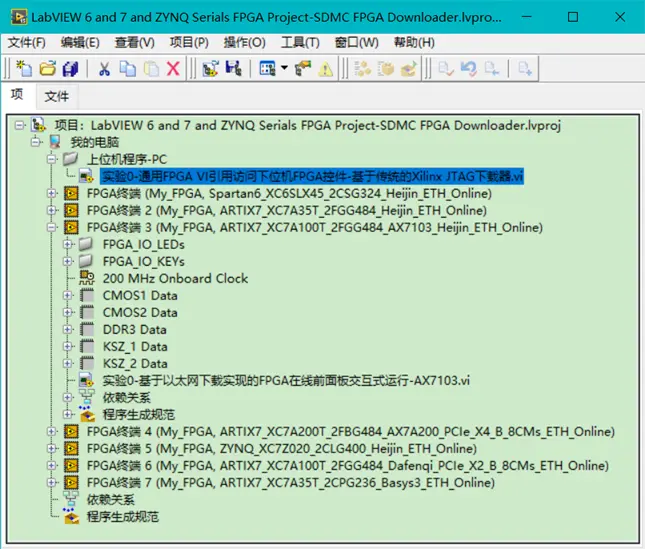

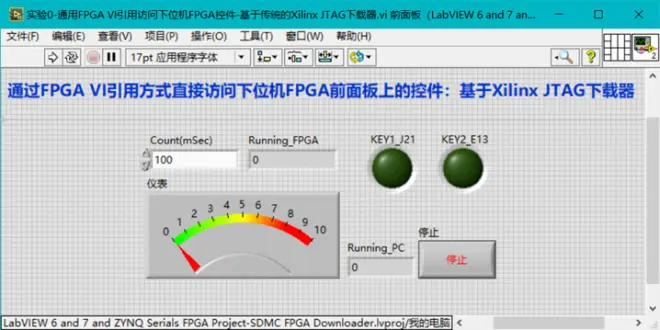

1)首先,新建一个空白的上位机LabVIEW VI程序,保存一下,命名为“实验0-通过FPGA VI引用访问下位机FPGA控件-基于传统的Xilinx JTAG下载器.vi”,如图5-294所示。

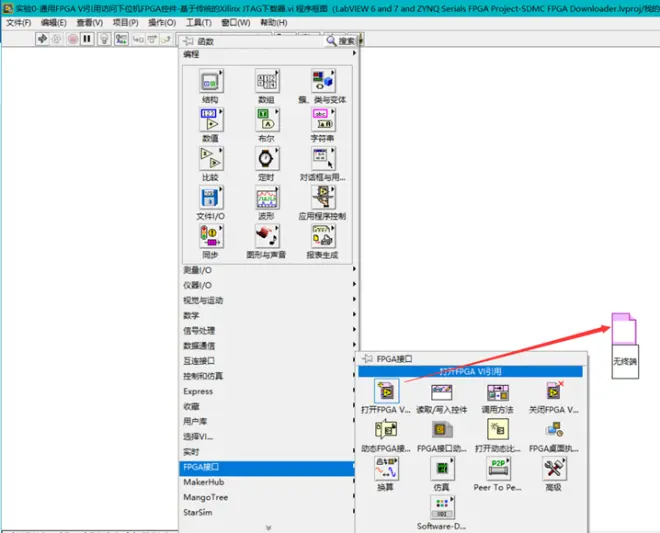

2)从“FPGA接口”函数选板里面,将第一个函数“打开FPGA VI引用”拖拽到程序框图里面,如图5-295所示。

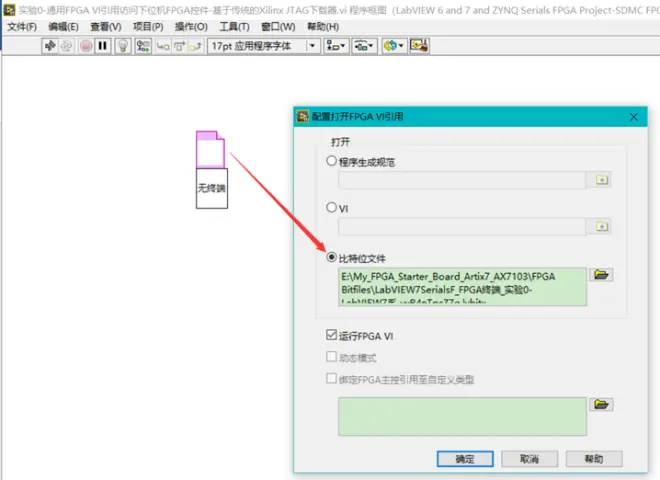

3)双击这个空白图标,在弹出来的对话框里面,选择“比特位文件”,然后点击右侧的“浏览”按钮找到先前我们编译好的AX7103 FPGA lvbitx文件,如图5-296所示。除了可以通过lvbitx位文件打开下位机FPGA程序,还可以选择上面的“程序生成规范”或者“VI”,一般情况下,都是建议通过打开lvbitx位文件最简单,最方便。

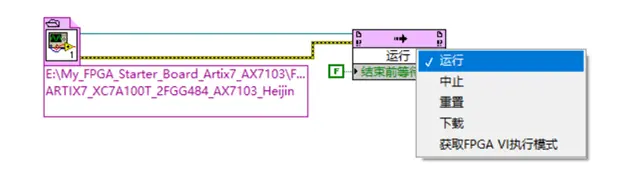

另外,对话框下方还有个“运行FPGA VI”复选框,默认是勾选的,我们也可以不勾选,直接在程序框图里面通过调用FPGA VI属性方法里面的“运行”来启动FPGA bit文件,如图5-297所示。

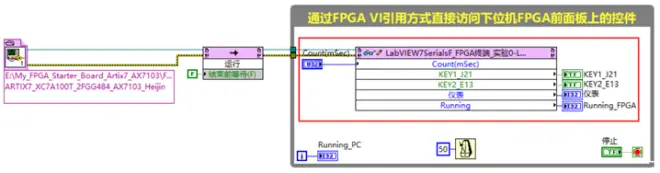

4)接着放置一个while循环,在循环里面通过调用“读取/写入控件”函数将下位机FPGA前面板上感兴趣的控件全部引出来,如图5-298所示。这样上位机程序就可以实时观察或者控制下位机FPGA VI前面板上的控件状态或者数值了。

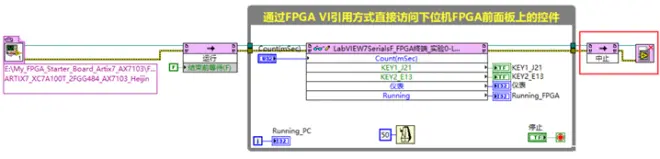

5)最后,在上位机程序关闭退出之前,需要将下位机FPGA bit文件停止运行,关掉FPGA引用释放资源,防止出现内存泄漏,如图5-299所示。

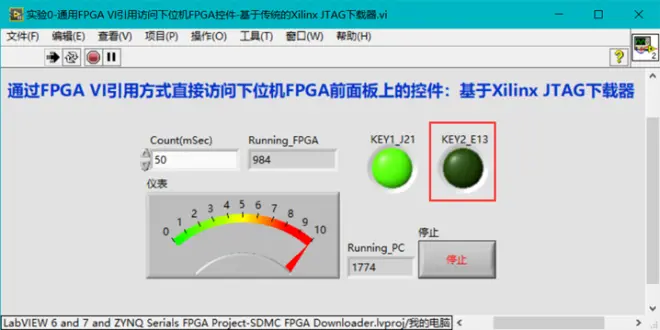

6)为了更形象的展示上位机可以通过FPGA VI引用的方式控制下位机FPGA前面板,我们将引出来的控件放在上位机界面上,如图5-300所示。

注意:这个界面是上位机LabVIEW应用程序前面板UI,不是下位机FPGA VI前面板,因为本节实验里面我们不需要下位机FPGA VI,只需要调用编译好的下位机FPGA lvbitx位文件即可。

5.7.1.3:实验现象(基于传统的Xilinx JTAG下载器实现的)

将黑金AX7103 FPGA开发板跟传统的Xilinx JTAG下载器连接好之后,上电,然后运行刚刚写好的上位机LabVIEW程序。此时,奇迹发生了,FPGA开发板上的4个LED闪烁了,闪烁频率5Hz,亮灭持续时间各100ms,如图5-301所示。

如果,我们在上位机程序前面板上将“Count(mSec)”控件里面的数值改成1000,FPGA开发板上的LED闪烁变慢了许多,只有0.5Hz频率闪烁,同时前面板上的“Running_FPGA”和“仪表”里面递增的速度也明显变慢了,如图5-302所示。说明上位机通过FPGA VI引用的方式成功的控制了下位机FPGA前面板上的控件。

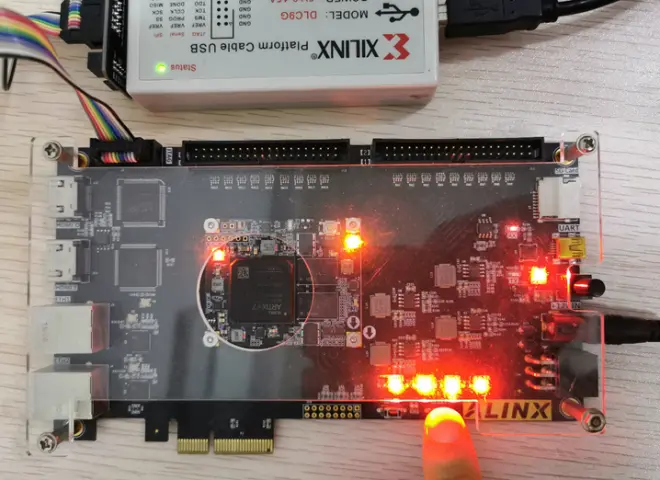

如果我们按住黑金AX7103开发板上的KEY2按键,如图5-303所示。那么上位机程序前面板上的KEY2指示灯会熄灭,如图5-304所示,说明上位机通过FPGA VI引用的方式捕捉到了下位机FPGA前面板上的指示灯控件状态。

至此,基于传统的Xilinx JTAG下载器验证了LabVIEW FPGA工具包里面重要的功能之一,通过FPGA VI引用的方式直接访问和控制下位机FPGA VI前面板上的控件,完全OK。

重大更新:需要提醒大家的是:我们是直接基于0成本的传统的Xilinx JTAG下载器实现这个功能的,没有对市面上的第三方FPGA板子做任何的改造,这个是我们与其他友商最大的不同!

因为,我们始终秉持“提供国产化、通用化、开源化的RIO解决方案”给广大用户,让这几十年里,市面上已有的海量的任意FPGA板子都能享受到图形化编程的乐趣,真正摆脱NI及其他友商限制,让自己的FPGA产品低成本量产成为可能性,并且牢牢抓紧FPGA里面的灵魂程序!

5.7.2:基于我们自研的以太网下载器实现上位机FPGA引用的方式访问下位机FPGA VI

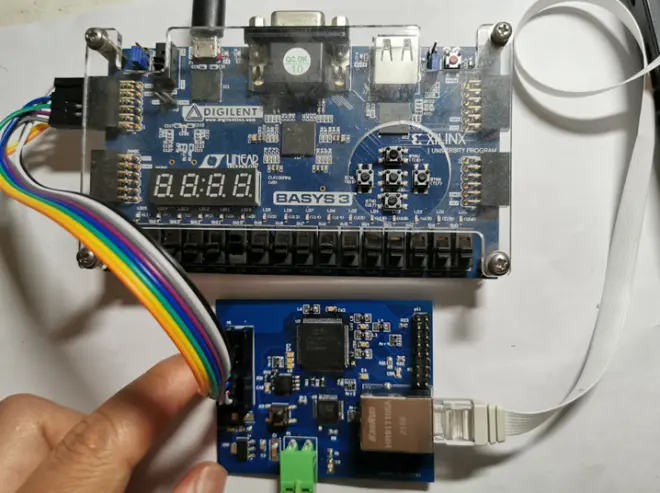

5.7.2.1:实验平台:以太网下载器+Digilent BASYS3 FPGA开发板(Artix7-35T)

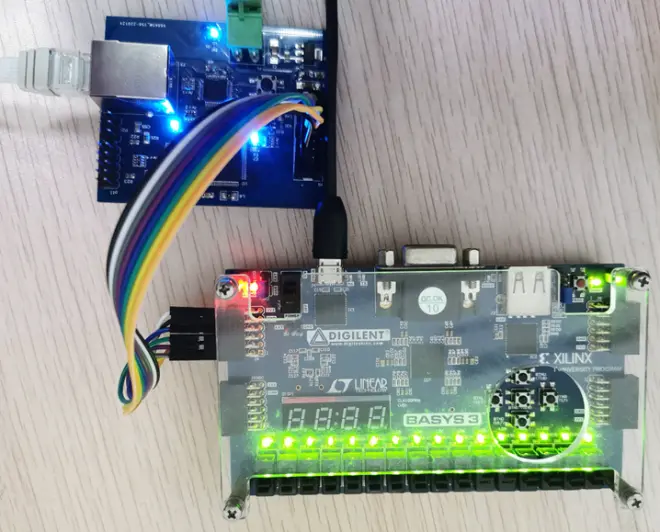

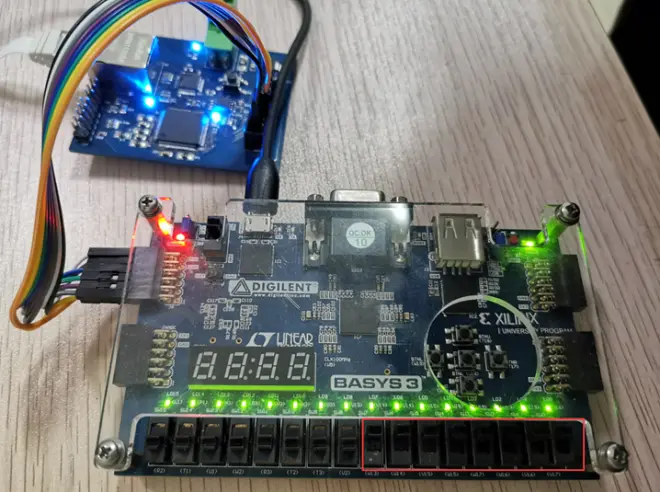

为了验证基于我们自研的SDMC FPGA Downloader以太网下载器也能通过上位机LabVIEW打开FPGA VI引用的方式来控制和访问下位机FPGA前面板上的控件,我们选取国外Digilent公司的BASYS3开发板来做测试,说明我们这套方案国内外通吃。

图5-305显示的是Digilent BASYS3 FPGA开发板与SDMC FPGA Downloader以太网下载器连接实物图。

5.7.2.2:上位机LabVIEW程序编写(调用FPGA VI引用方式)

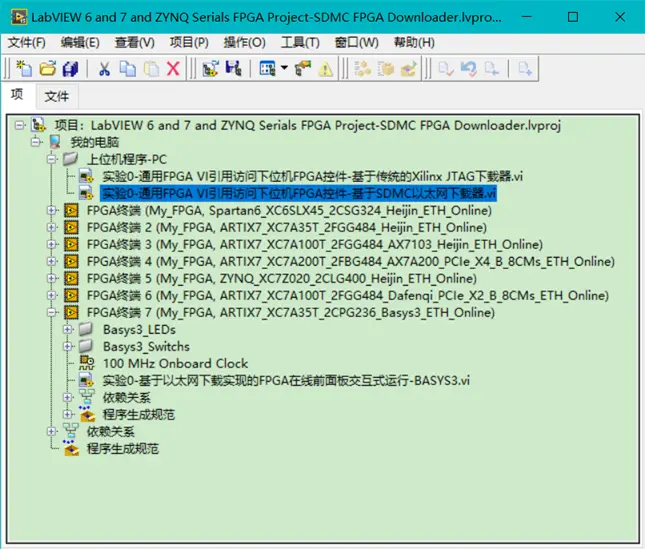

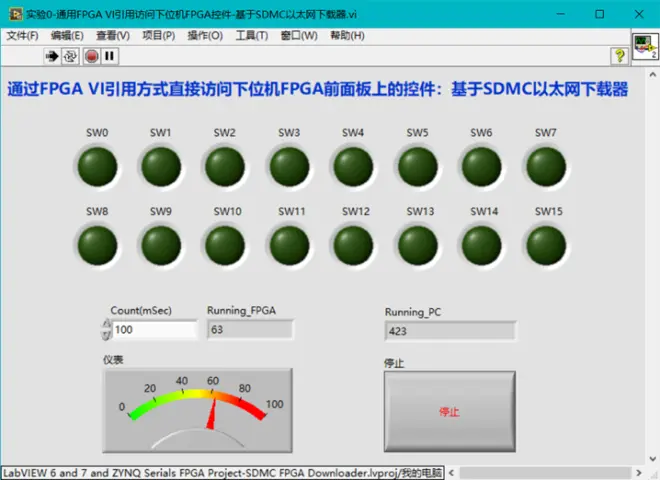

1)首先,新建一个空白的上位机LabVIEW VI程序,保存一下,命名为“实验0-通过FPGA VI引用访问下位机FPGA控件-基于SDMC以太网下载器.vi”,如图5-306所示。

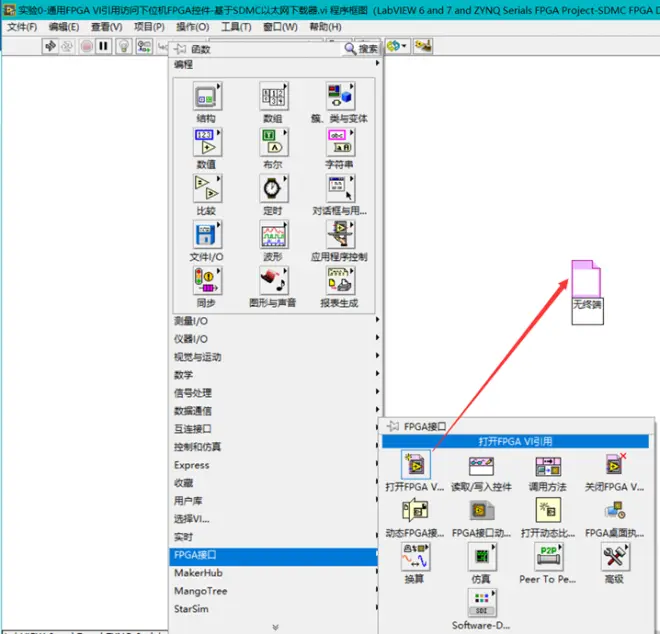

2)从“FPGA接口”函数选板里面,将第一个函数“打开FPGA VI引用”拖拽到程序框图里面,如图5-307所示。

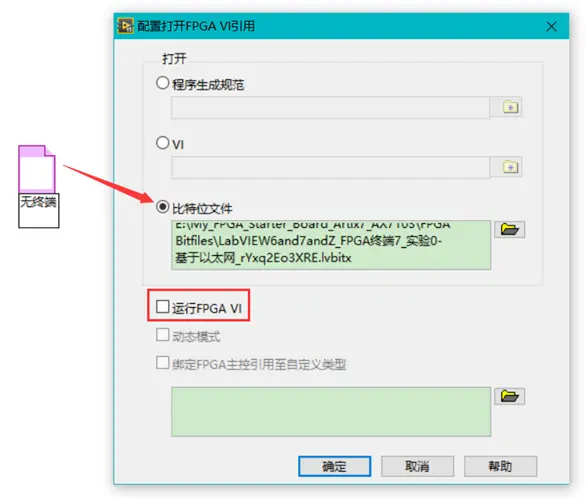

3)双击这个空白图标,在弹出来的对话框里面,选择“比特位文件”,然后点击右侧的“浏览”按钮找到先前我们编译好的BASYS3 FPGA lvbitx文件,如图5-308所示。除了可以通过lvbitx位文件打开FPGA程序,还可以选择上面的“程序生成规范”或者“VI”,一般情况下,都是建议通过打开lvbitx位文件最简单,最方便。

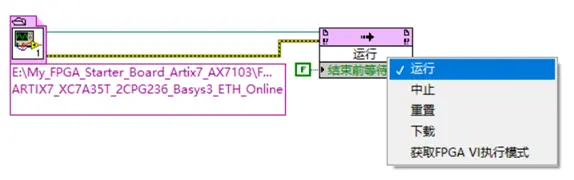

另外,对话框下方还有个“运行FPGA VI”复选框,默认是勾选的,我们也可以不勾选,直接在程序框图里面通过调用FPGA VI属性方法里面的“运行”来启动FPGA bit文件,如图5-309所示。

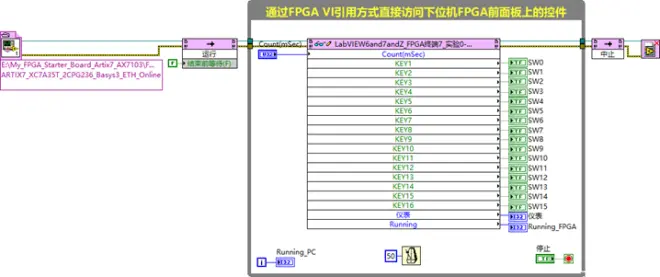

4)接着放置一个while循环,在循环里面通过调用“读取/写入控件”函数将下位机FPGA前面板上的感兴趣的控件全部引出来,如图5-310所示。这样上位机程序就可以实时观察或者控制下位机FPGA前面板上的控件状态或者数值了。

5)最后,当上位机程序关闭退出之前,需要将下位机FPGA bit程序停止运行,关掉FPGA引用释放资源,防止出现内存泄漏,如图5-311所示。

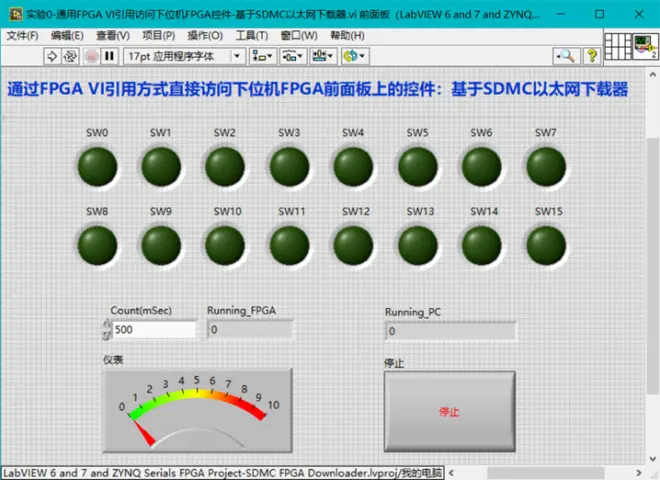

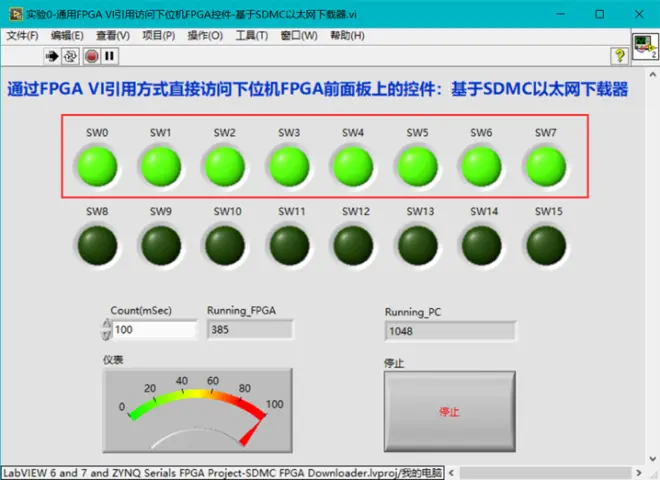

6)为了更形象的展示上位机可以通过FPGA VI引用的方式控制下位机FPGA前面板,我们将引出来的控件放在上位机界面上,如图5-312所示。

注意:这个界面是上位机LabVIEW应用程序前面板UI,不是下位机FPGA VI前面板,因为本节实验里面我们不需要下位机FPGA VI,只需要调用编译好的下位机FPGA lvbitx位文件即可。

5.7.2.3:实验现象(基于我们自研的SDMC以太网下载器实现的)

将Digilent BASYS3 FPGA开发板跟SDMC以太网下载器连接好之后,上电,然后运行刚刚写好的上位机LabVIEW程序。此时,奇迹发生了,FPGA开发板上的16个LED闪烁了,闪烁频1Hz,亮灭持续时间各500ms,如图5-313所示。

如果,我们在上位机程序前面板上将“Count(mSec)”控件里面的数值改成100,FPGA开发板上的LED灯闪烁频率明显变快了许多,按照5Hz进行闪烁;同时前面板上的“Running_FPGA”和“仪表”里面递增的速度也同样变快了,如图5-314所示。说明上位机通过FPGA VI引用的方式成功的控制了下位机FPGA前面板上的控件。

如果我们将Digilent BASYS3 FPGA开发板上的Switch拨码开关里面的前8个sw0~sw7拨上去,如图5-315所示。那么上位机程序前面板上的第一行8个指示灯全部点亮,如图5-316所示,说明上位机通过FPGA VI引用的方式捕捉到了下位机FPGA前面板上的指示灯控件状态。

至此,基于以太网下载器验证了LabVIEW FPGA工具包里面重要的功能之一,通过FPGA VI引用的方式直接访问和控制下位机FPGA VI前面板上的控件,完全OK。

需要提醒大家的是:这里我们提供的第二种方法,那就是直接基于我们自研的SDMC FPGA Downloader以太网下载器实现这个功能的,并没有对市面上的第三方FPGA板子做任何的改造,这个也是我们与其他友商最大的不同!

因为,我们始终秉持“提供国产化、通用化、开源化的RIO解决方案”给广大用户,让这几十年里,市面上已有的海量的任意FPGA板子都能享受到图形化编程的乐趣,真正摆脱NI及其他友商限制,让自己的FPGA产品低成本量产成为可能性,并且将FPGA芯片里面的灵魂程序掌握在自己手里!