【2019版】3.3.3 存储器基本概念 P62 - 00:12

【2019版】3.1-3.2 主存简单模型和寻址概念 P59 - 07:35

存储元->存储单元->存储体

【2019版】3.1-3.2 主存简单模型和寻址概念 P59 - 09:06

字节:Byte

1Byte=8bit

【2019版】3.1-3.2 主存简单模型和寻址概念 P59 - 13:00

片选线:高电平有效,低电平有效,确定那个存储芯片被选中(作用:开关)

【2019版】3.1-3.2 主存简单模型和寻址概念 P59 - 14:08

存储器芯片结构

【2019版】3.1-3.2 主存简单模型和寻址概念 P59 - 19:20

数据线数和地址线数共同反映存储芯片容量大小

如:地址线10根,数据线8根,则芯片容量=2^10*8=8k位(bit)

【2019版】3.3.1 半导体存储器RAM P60 - 07:48

RAM:随机存取存储器,特点:断电丢失信息

SRAM:静态随机存取存储器

常用作高速缓存

DRAM:动态随机存取存储器

常用作主存

DRAM的刷新:集中刷新,分散刷新,异步刷新

【2019版】3.3.2 半导体存储器ROM P61 - 06:44

ROM:只读存储器(断电不丢失)

主存容量扩展

位扩展:

字扩展:

译码器

作用:将主存的n条数据线转变为能控制2^n个芯片

【2019版】3.4.1 主存与CPU的连接 P63 - 17:30

【2019版】3.4.1 主存与CPU的连接 P63 - 19:49

字位同时扩展

【2019版】3.4.1 主存与CPU的连接 P63 - 25:16

【2019版】3.4.2 主存与CPU的连接-例题 P64 - 00:09

英文字母加上面一条横线,意思是低电平有效

系统程序区用ROM,用户程序区用RAM

图中8根数据线表示用8位

现在所求的是地址线

【2019版】3.4.2 主存与CPU的连接-例题 P64 - 06:44

如题给出地址,则先用大减小,将所得结果转化为二进制,目的是求出地址线根数

【2019版】3.4.2 主存与CPU的连接-例题 P64 - 08:36

做题技巧

- 确认数据线,地址线(几根数据线就需要几位,先求地址线)

- 分析地址空间

- 选择存储芯片

【2019版】3.6.1 局部性原理及性能分析 P66 - 13:21

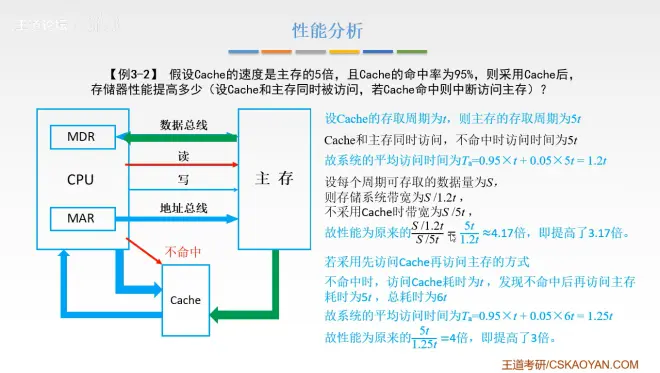

主存系统平均访问时间:

注:命中率为CPU访问的信息在catch中的比率

Ta=命中率*访问catch的时间+(1-命中率)*访问主存的时间

【2019版】3.6.1 局部性原理及性能分析 P66 - 16:50

【2019版】3.6.1 局部性原理及性能分析 P66 - 18:13

【2019版】3.6.2 Cache-地址映射 P67 - 07:45

主存放到Catch中的哪个位置:

空位随意放:全相联映射

对号入座:直接映射

分组,组内随意放:组相联映射

【2019版】3.6.4 Cache例题替换版 P69 - 06:34

替换算法

全相联映射:

主存字块标记=主存地址空间大小-每个Catch块大小

每次Catch调用一个Catch块的数据,如:0000~1111占一个Catch块

【2019版】3.6.4 Cache例题替换版 P69 - 13:17

直接映射:

相比于全相联映射多了个Catch字块地址,在进行Catch调用时,判断是否命中需要比较主存字块标记和Catch字块地址,如Catch字块地址相同,主存字块标记不同,则直接替换Catch里相对应的位置

组相联映射:

【2019版】3.6.4 Cache例题替换版 P69 - 20:39

【2019版】3.6.4 Cache例题替换版 P69 - 29:54

指令系统

【2019版】4.1 指令格式 P71 - 13:25

【2019版】4.1 指令格式 P71 - 18:23

扩展操作码

当为1111时,三地址扩展为2地址

【2019版】4.2.1 指令寻址 P72 - 08:29

机器字长:CPU一次能处理的二进制数据的位数

指令字长:一个指令字中包含的二进制代码的位数

存储字长:一个存储单元存储二进制代码的长度

【2019版】4.2.2 数据寻址1 P73 - 06:42

【2019版】4.2.1 指令寻址 P72 - 13:45

指令寻址:下一条指令的指令地址

数据寻址:确定本条指令的操作数地址

【2019版】4.2.2 数据寻址1 P73 - 08:17

立即寻址:形式地址为操作数本身,又称为立即数,一般采用补码的形式,共访存一次

【2019版】4.2.2 数据寻址1 P73 - 11:08

直接寻址:指令字中的形式地址就是操作数的真实地址,即:EA=A

共访存两次

【2019版】4.2.2 数据寻址1 P73 - 13:27

间接寻址:指令字给出的是操作数地址的地址

即EA=(A)

共访存三次

【2019版】4.2.2 数据寻址1 P73 - 18:38

寄存器寻址:在指令字中直接给出操作数的寄存器编号

【2019版】4.2.2 数据寻址1 P73 - 26:37

【2019版】4.2.3 数据寻址2——偏移寻址 P74 - 01:26

基址寻址:将cpu中的基址寄存器(BR)的内容加上指令格式中的形式地址A,而形成操作数的有效地址,即EA=(BR)+A

特点:面向操作系统

【2019版】4.2.3 数据寻址2——偏移寻址 P74 - 11:44

变址寻址:有效地址EA等于指令字中的形式地址A与变址寄存器IX的内容相加之和,即EA=(IX)+A,其中IX为变址寄存器(专用),也可用通用寄存器作为变址寄存器

特点:面向用户

【2019版】4.2.3 数据寻址2——偏移寻址 P74 - 21:18

相对寻址:把程序计数器PC的内容加上指令格式中的形式地址A而形成操作数的有效地址,即:

EA=(PC)+A,其中A是相对于当前指令地址的位移量,可正可负,补码表示

【2019版】4.2.3 数据寻址2——偏移寻址 P74 - 31:13

【2019版】4.2.4 数据寻址3——堆栈寻址 P75 - 01:22

堆栈寻址:操作数存放在堆栈中,隐含使用堆栈指针作为操作数地址

特点:后进先出

【2019版】4.3 CISC和RISC替换版 P76 - 05:55

【2019版】5.1 CPU的功能和基本结构 P77 - 00:44

【2019版】5.1 CPU的功能和基本结构 P77 - 03:02

【2019版】5.1 CPU的功能和基本结构 P77 - 05:02

【2019版】5.1 CPU的功能和基本结构 P77 - 18:53

【2019版】5.2 指令周期的数据流 P78 - 02:06

指令周期:CPU从主存中每取出并执行一条指令所需的全部时间

【2019版】5.2 指令周期的数据流 P78 - 03:45

【2019版】5.2 指令周期的数据流 P78 - 24:33

单指令周期

多指令周期

流水线方案

【2019版】5.3.1 数据通路1——CP... P79 - 18:58

【2019版】5.3.2 数据通路2——专用数据通路 P80 - 04:45

【2019版】5.4.2 控制器2——微程序 P82 - 21:41

直接编码

字段直接编码

【2019版】5.4.2 控制器2——微程序 P82 - 24:38

(了解)字段间接编码(隐式编码)

【2019版】5.4.2 控制器2——微程序 P82 - 34:36

微命令是微操作的控制信号

微操作是微命令的执行过程

微指令是微命令的集合

微周期是控制存储器中取出一条伪指令并执行所需的时间

【2019版】5.5.1 指令流水线的概... P83 - 07:18

指令流水

总线

特点:分时,共享

数据总线(DB)

地址总线(AB)

控制总线(CB)

按总线功能分:

片内总线:CPU芯片内部寄存器与寄存器之间,寄存器与ALU之间的公共连接线

系统总线:DB,AB,CB

通信总线(外部总线)

【2019版】7.4.1 程序查询方式 P94 - 00:36

【2019版】7.4.1 程序查询方式 P94 - 01:34

程序中断机制

【2019版】7.4.2 中断系统 P95 - 11:59

【2019版】7.4.2 中断系统 P95 - 33:23

【2019版】7.4.2 中断系统 P95 - 42:30

【2019版】7.4.3 程序中断方式 P96 - 00:31

程序中断作用

DMA控制

标签: