FPGA设计时序约束八、others类约束之Set_Case_Analysis

一、序言

在Vivado的时序约束窗口中,存在一类特殊的约束,划分在others目录下,可用于设置忽略或修改默认的时序路径分析,以Vivado2022.1版本为例,主要包括以下4类

二、Set Case Analysis

2.1 基本概念

Set case analysis(设置案例分析)命令通常通过对逻辑如配置寄存器设置常数值来描述功能模块,设置对象可为端口,线net,层级引脚或子模块输入引脚,常数值通过约束的逻辑单元传输,从而关闭该单元的任何时序分析,功能和设置set false path类似。约束可以在SDC、XDC文件中使用。

使用set case analysis可以减少分析的空间,运行时间和内存消耗,将信号是一个常量值的信息告知时序分析工具是很重要的,对于保证不去报告非功能路径和不相关的路径也是至关重要的。因此,一个引脚pin带有set_case_anlaysis约束时,上面传输的信号是不活跃信号,和引脚相关的时序arc是关闭的。

最常见的使用场景是对一个多路选择器选择引脚设置为0或1,使得两个多路选择器中一个输入来传输,以关闭从mux/s到mux/I1引脚的时序分析路径为例,约束命令如下

再看一个例子,将一个AND门 的一个输入通过set_case_analysis设为0,AND门的输出也为0,即0传输到了下一逻辑,时序分析工具不会去计算对应的时序arch也不会展示在时序报告中。但是,布局布线中仍会去修复这些引脚上的最大切换,最大扇出违例。

2.2 设置界面

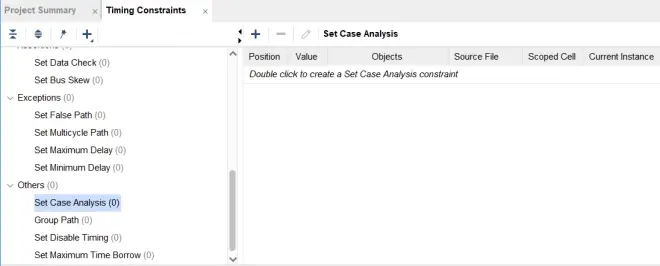

进入Timing Constraints界面,在左侧Others栏中选中Set Case Analysis,右侧即显示Set Case Analysis界面,双击空白位置

在Find names of type的下拉框显示可设置的对象,有Port和Cell pins两类

可约束的值有4个:0,1,rising,falling,约束为0或1时,对应的时序路径将不存在,设置为切换边沿时,只有信号为设置的边沿切换时才进行时序分析。

2.3 命令语法

命令格式如下

参数含义如下表

2.4 命令示例

约束两个主时钟到CLKBUFGMUX的两个输入引脚上,将set_case_analysis约束选择引脚clock_sel/S的值为1,此时将只有clk_B会传输到输出端口,clk_A被阻断了,效果和将对应的pin连接到VDD或VSS相同。。

三、工程示例

工程代码:

综合后网表连接图

未添加set_case_analysis时的时序报告,同步时钟报告中只有clk4,异步时钟报告中有clk1到clk2,clk2到clk3的时序路径,根据综合网表连接图,符合预期。

对clk1设置set_case_analysis值为fall,clk4设置set_case_analysis值为1,同步时钟路径中已不存在clk4,异步时钟路径中存在clk1到clk2。因为clk1设置的analysis clk为下降沿,而实际为上升沿,clk4设置为常量1,不存在切换

四、参考资料

1、用户手册《ug835-vivado-tcl-commands-en-us-2023.1.pdf》

文档链接:https://pan.baidu.com/s/1Su_w9CDHR7R9_tt_in_arQ?pwd=7w4f

提取码:7w4f

2、Vivado的command reference