3.9VGA显示矩阵--明德扬科教(2)(mdy-edu.com)

接3.9VGA显示矩阵--明德扬科教(1)(mdy-edu.com)

第4节 综合与上板4.1 新建工程

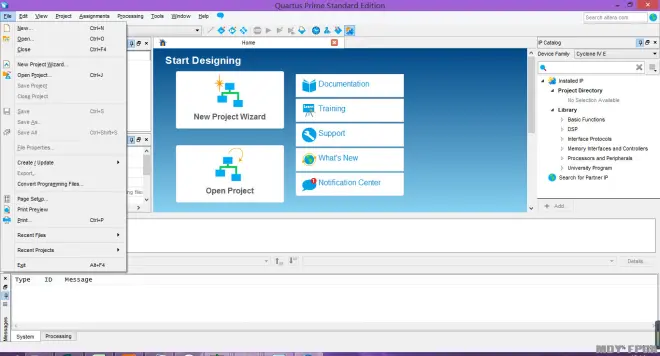

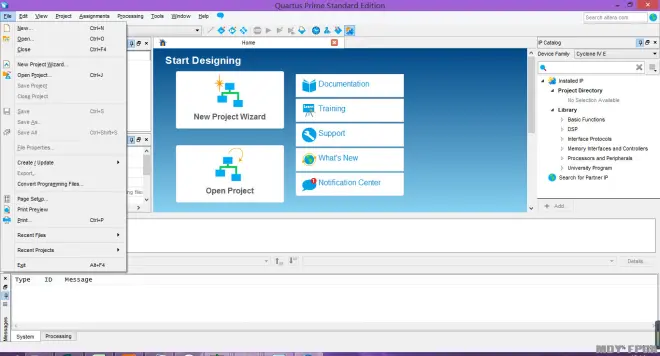

打开软件Quartus Ⅱ,点击“File”下拉列表中的New Project Wzard...新建工程选项,如下图所示。

图3.9-11Quartus新建工程

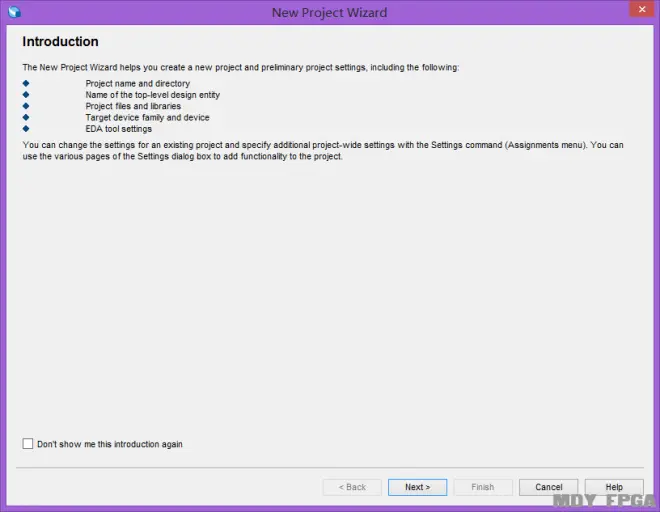

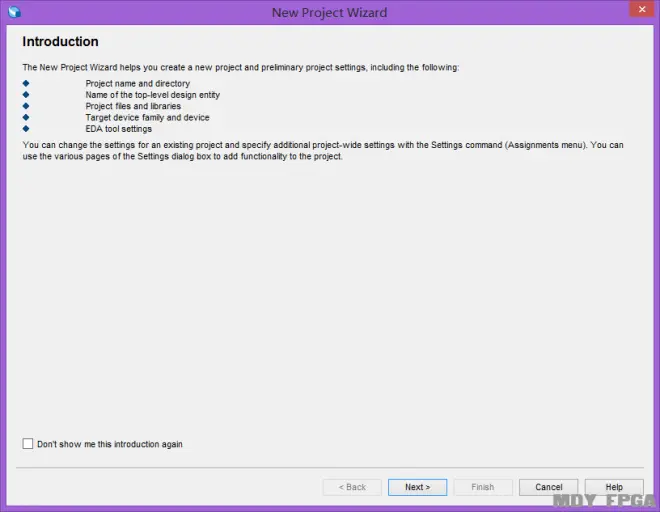

随后会出现Quartus新建工程介绍,如下图所示,直接点击“Next”。

图3.9-12Quartus新建工程介绍

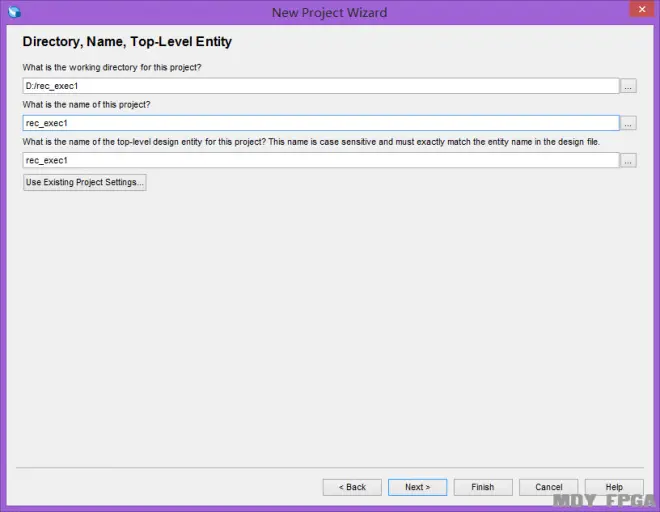

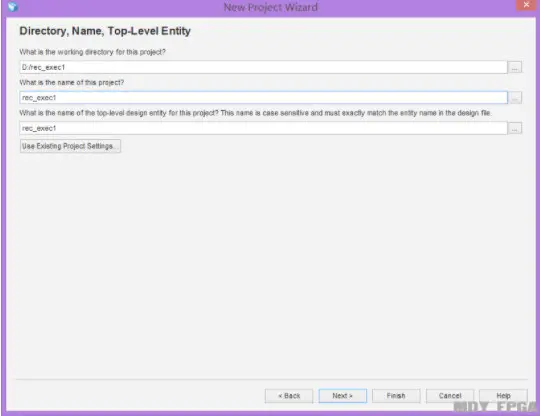

此时会出现工程文件夹、工程名、顶层模块名设置界面,如图3.9- 13所示。设置目录为:D:/mdy_book/rec_exec1,工程名和顶层名为rec_exec1。再次强调,为了避免初学者在后续操作中发生程序跳出未知错误的问题,强烈建议设置的文件目录和工程名称与本书保持一致。设置完成后点击“Next”。

图3.9-13QUARTUS新建工程设置名称

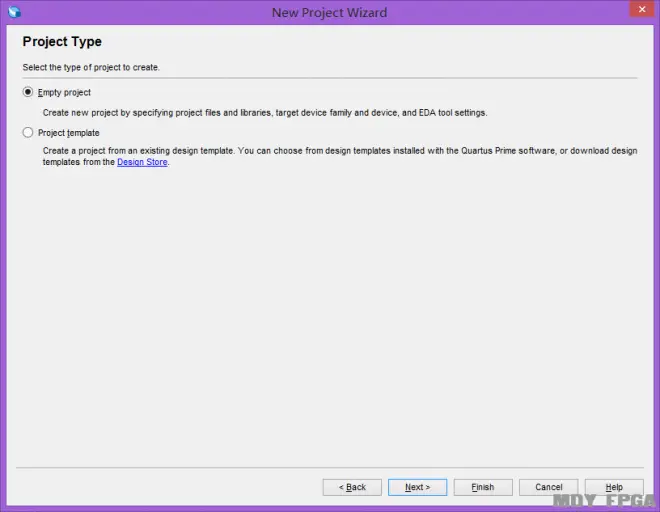

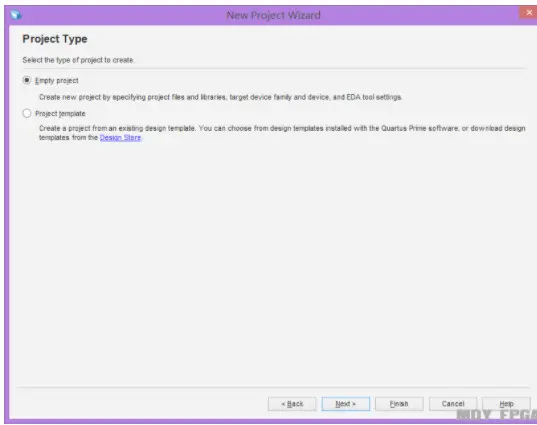

新建工程类型设置如下图所示,选择“Empty project”,然后点击“Next”。

图3.9-14QUARTUS新建工程类型

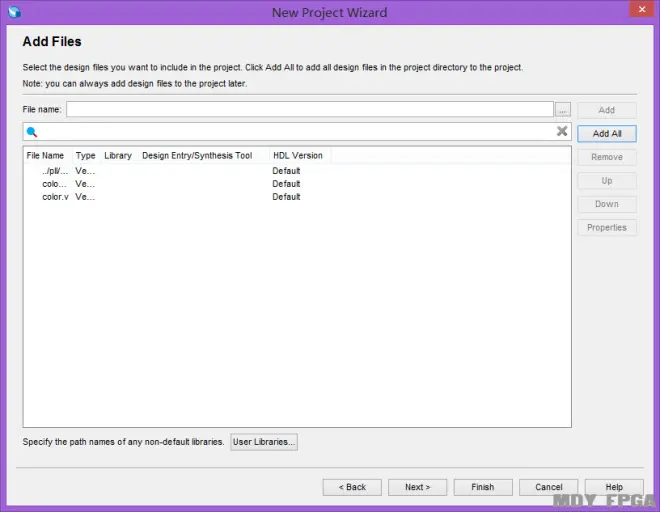

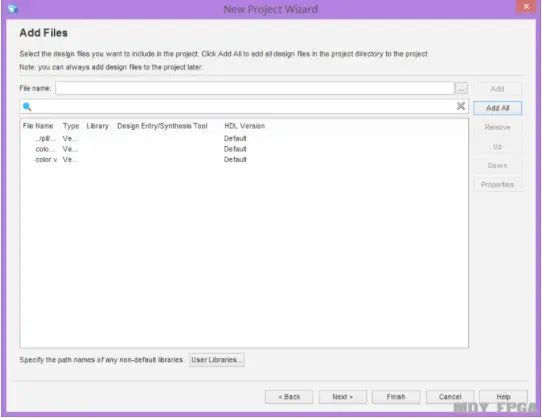

接下来进行文件添加,其界面如下图所示。点击右侧的“Add”按钮,选择之前写好的“rec_exec1.v”文件,可以看到界面下方会显示出文件,之后点击“Next”。

图3.9-15QUARTUS添加文件

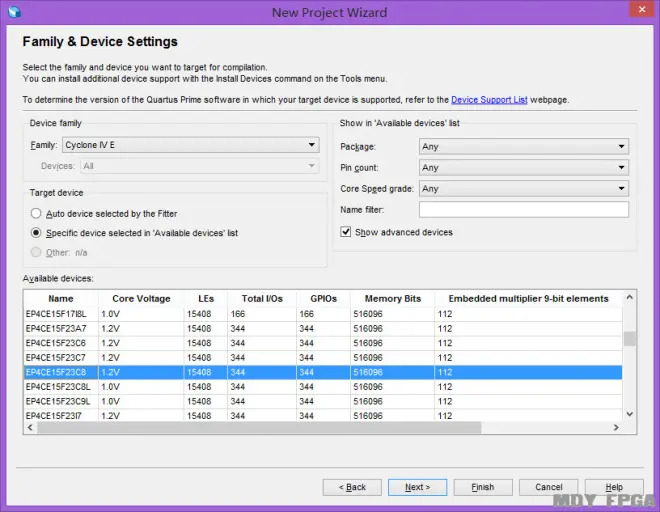

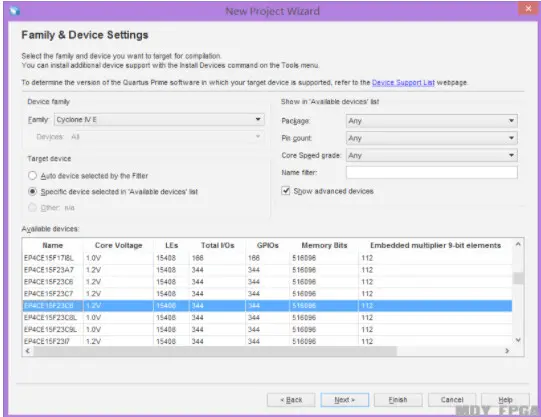

图3.9-16为芯片选择页面,选择“Cyclone ⅣE”,在芯片型号选择处选择“EP4CE15F23C8”,之后点击“Next”。

图3.9-16QUARTUS选择芯片型号

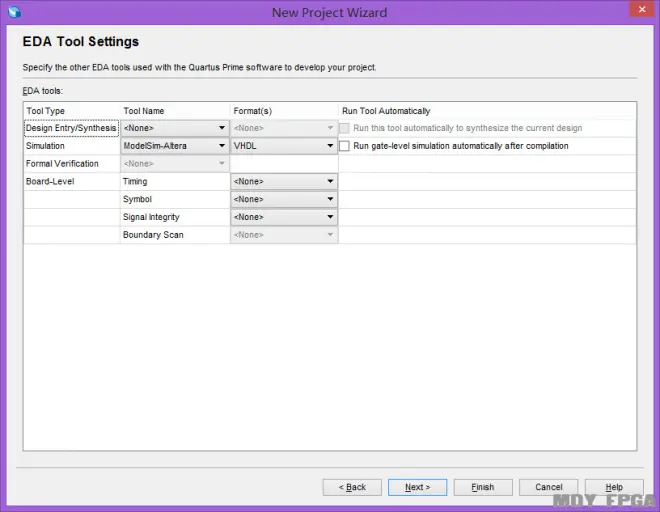

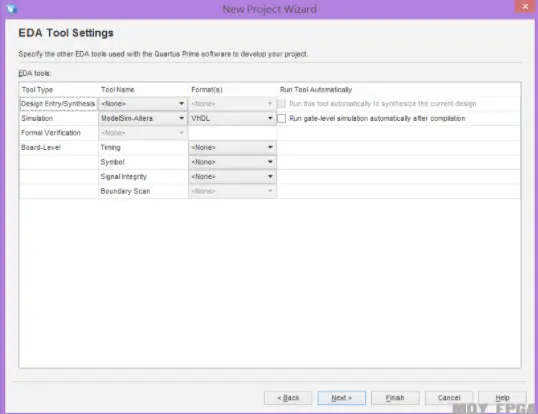

图3.9- 17为QUARTUS设置工具界面,不必做任何修改,直接点击“Next”。

图3.9-17QUARTUS设置工具界面

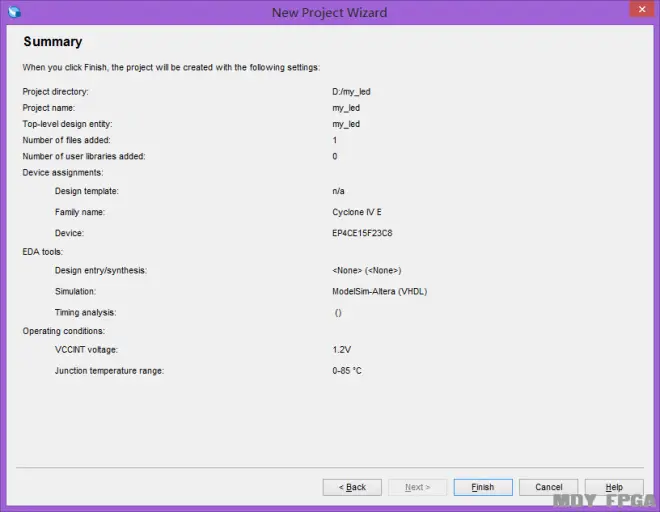

下图为QUARTUS新建工程汇总界面,可以看到新建工程的汇总情况,点击“Finish”完成新建工程。

图3.9-18QUARTUS新建工程汇总界面

4.2 综合

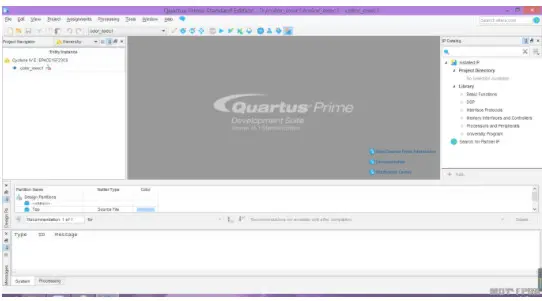

新建工程步骤完成后,就会出现如下图所示的 QUARTUS新建工程后界面。

图3.9-19QUARTUS新建工程后界面

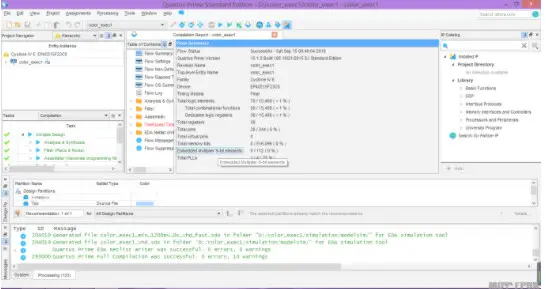

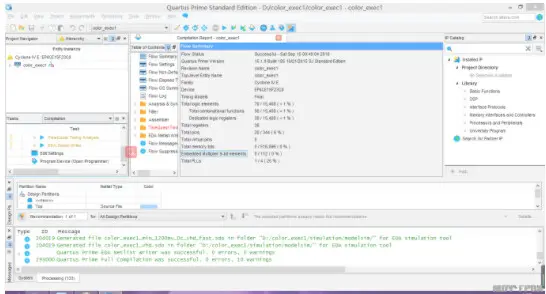

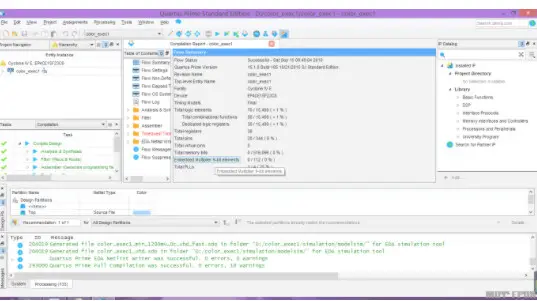

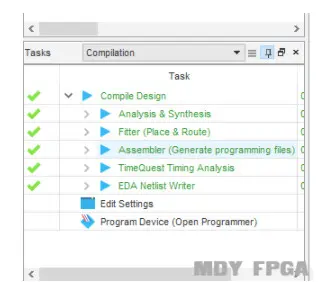

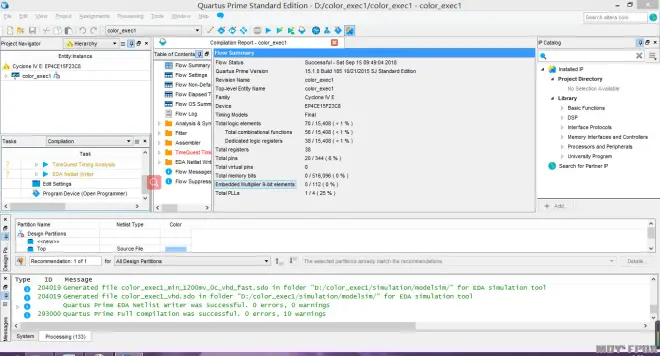

点击编译按钮,可以对整个工程进行编译。编译成功的界面如下图所示。

图3.9-20QUARTUS编译后界面

4.3 配置管脚

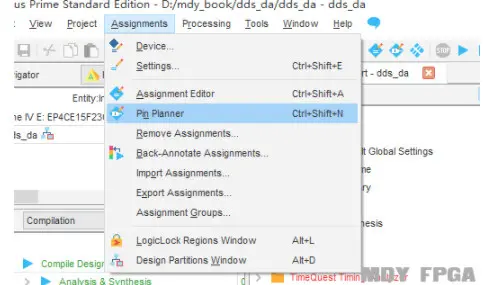

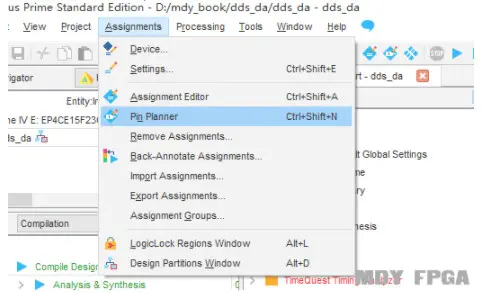

下面需要对相应管脚进行配置。如下图所示,在菜单栏中选中“Assignments”,然后选择“Pin Planner”,随后就会弹出配置管脚的窗口。

图3.9-21QUARTUS配置管脚选项

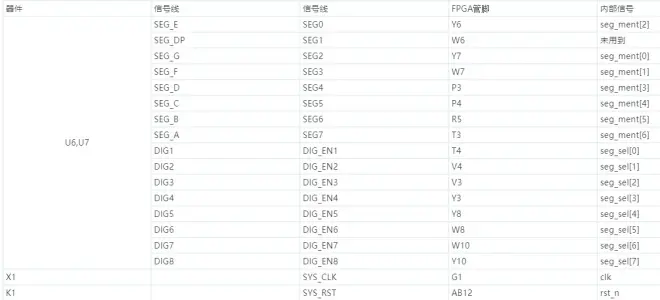

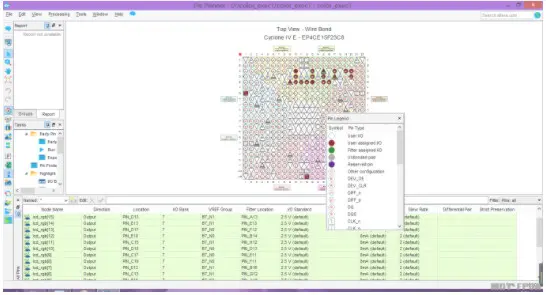

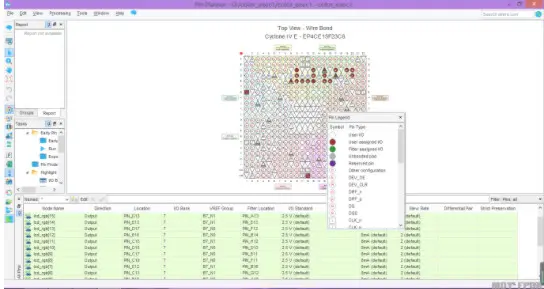

在配置窗口最下方中的“location”一列,参考信号和管脚关系,按照表3.9- 2中最右两列配置好FPGA管脚,配置管理来源参见管脚配置环节,最终配置的结果如图3.9-22。配置完成后,关闭Pin Planner,软件自动会保存管脚配置信息。

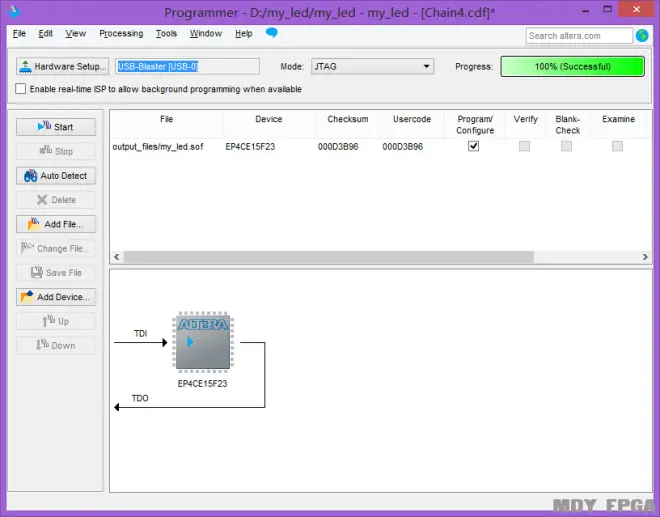

表3.9 - 2信号和管脚关系

图3.9-22 QUARTUS配置管脚

4.4 再次综合

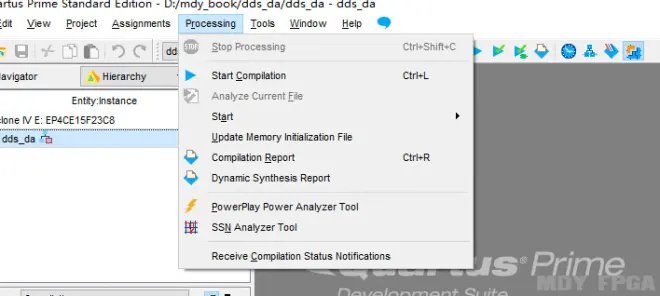

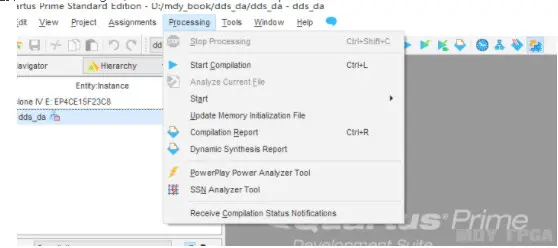

再次打开“QUARTUS”软件,在菜单栏中选中“Processing”,然后选择“Start Compilation”,再次对整个工程进行编译和综合,如图3.9- 23所示。

图3.9-23QUARTUS编译选项

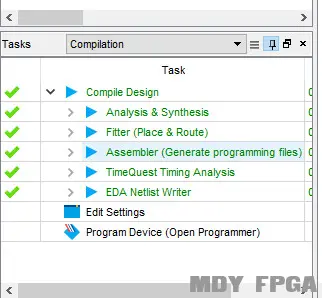

当出现如下图所示的QUARTUS编译成功标志则说明编译综合成功。

图3.9-24QUARTUS编译成功标志

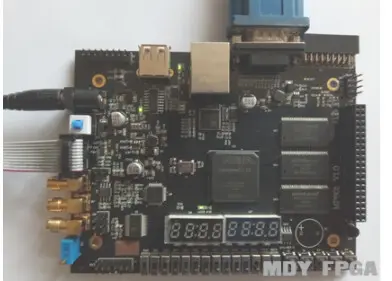

4.5 连接开发板

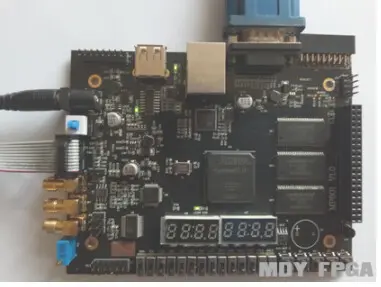

完成编译后开始进行上板调试操作,按照下图的方式将下载器接入电脑USB接口,接上开发板电源,将开发板的VGA口连接到一台显示器上,然后按下下方蓝色开关,硬件连接完毕。

图3.9-25开发板连接图

4.6 上板

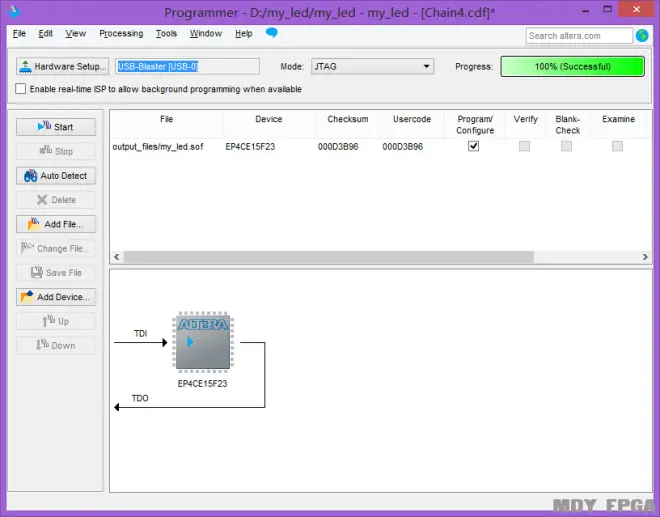

打开QUARTUS界面,单击界面中的“file:///C:UsersxkdnAppDataLocalTempksohtml9492wps69.jpg”,则会弹出配置界面。在界面中点击“add file”添加“.sof”文件后点击“Start”,会在“Progress”出现显示进度。

图3.9-26QUARTUS界面

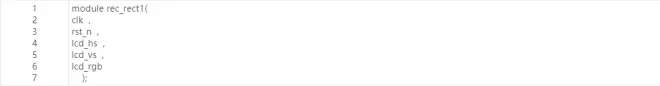

QUARTUS下载程序界面如下图所示,当进度条到100%提示成功后,即可在显示器上观察到相应的现象。

图3.9-27QUARTUS下载程序界面

进度条提示成功后,如果操作无误此时可以在显示器上看到红色区域外框与绿色区域结合的矩阵显示。如果没有显示成功,就需要返回检查一下连接是否到位,代码是否编写正确。如果无法自己完成错误排查的话,可以重新按照步骤操作一遍,相信一定会达到想要的效果。

第5节 简化版步骤分享

这里依旧会分享简化版的步骤,方便掌握基础原理后进行反复操作复习。

5.1 设计实现5.1.1 顶层接口

新建目录:D:mdy_book ec_exec1。在该目录中,新建一个名为rec_exec1.v的文件,并用GVIM打开,开始编写代码。

确定顶层信号,信号和管脚的对应关系见表3.9- 2。

表3.9 –2 信号和管脚关系

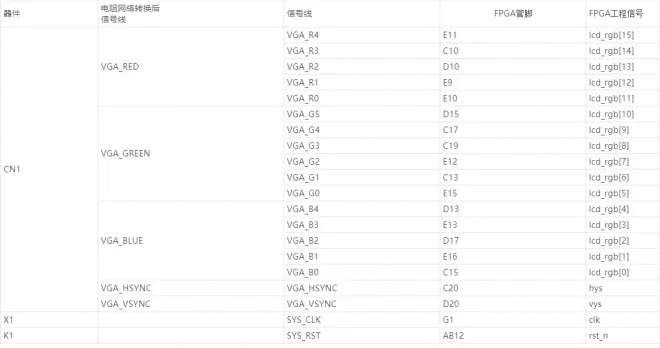

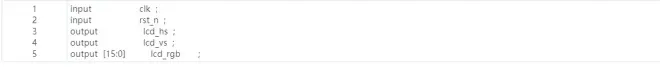

写出顶层信号代码:

声明输入输出属性:

5.1.2 信号设计

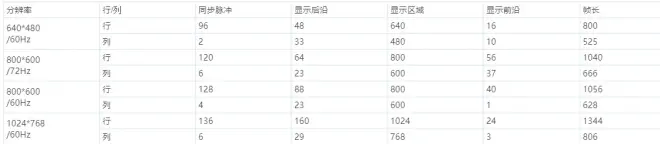

首先进行架构设计。设计目标中确定显示器中需要显示640*480分辨率的图像,因此使用下表中的第一种分辨率。

表3.9–1 VGA常用分辨率

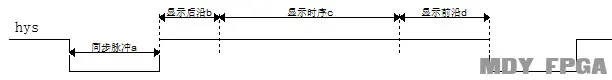

分析设计目标可得VGA行同步信号,其时序图如下所示。

图3.9-3VGA行同步信号时序

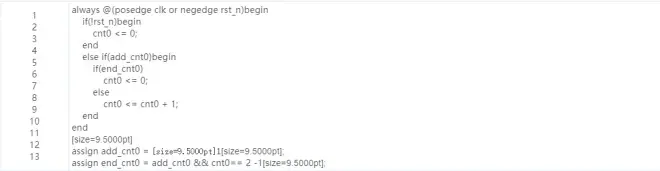

设计计数器架构,表示计数基准时间的计数器cnt0代码如下:

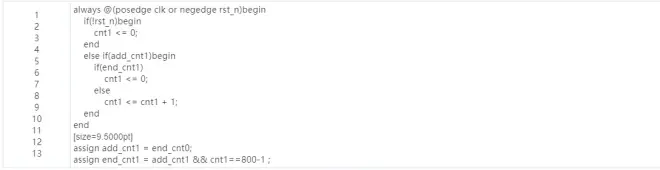

表示计数hys长度的计数器cnt1代码如下:

设计行同步信号的代码如下:

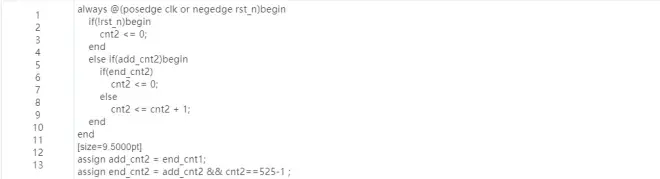

设计VGA场同步时序计数器cnt2代码如下:

设计场同步信号的代码如下:

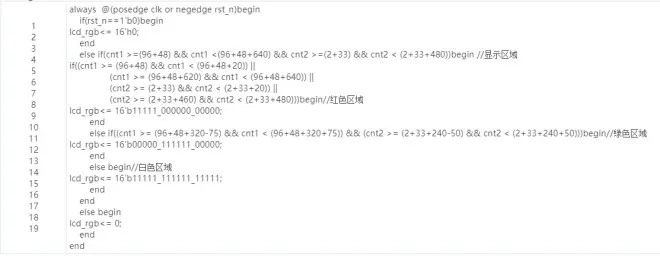

设计lcd_rgb信号代码如下:

至此,主体程序已经完成,接下来将module补充完整。

5.1.3 信号定义

首先定义信号类型,cnt0、add_cnt0 和 end_cnt0的信号定义如下:

cnt1的信号定义如下:

add_cnt1和end_cnt1的信号定义如下:

cnt2的信号定义如下:

add_cnt2和end_cnt2的信号定义如下:

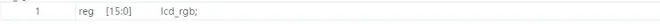

lcd_rgb的信号定义如下:

hys和vys代码如下:

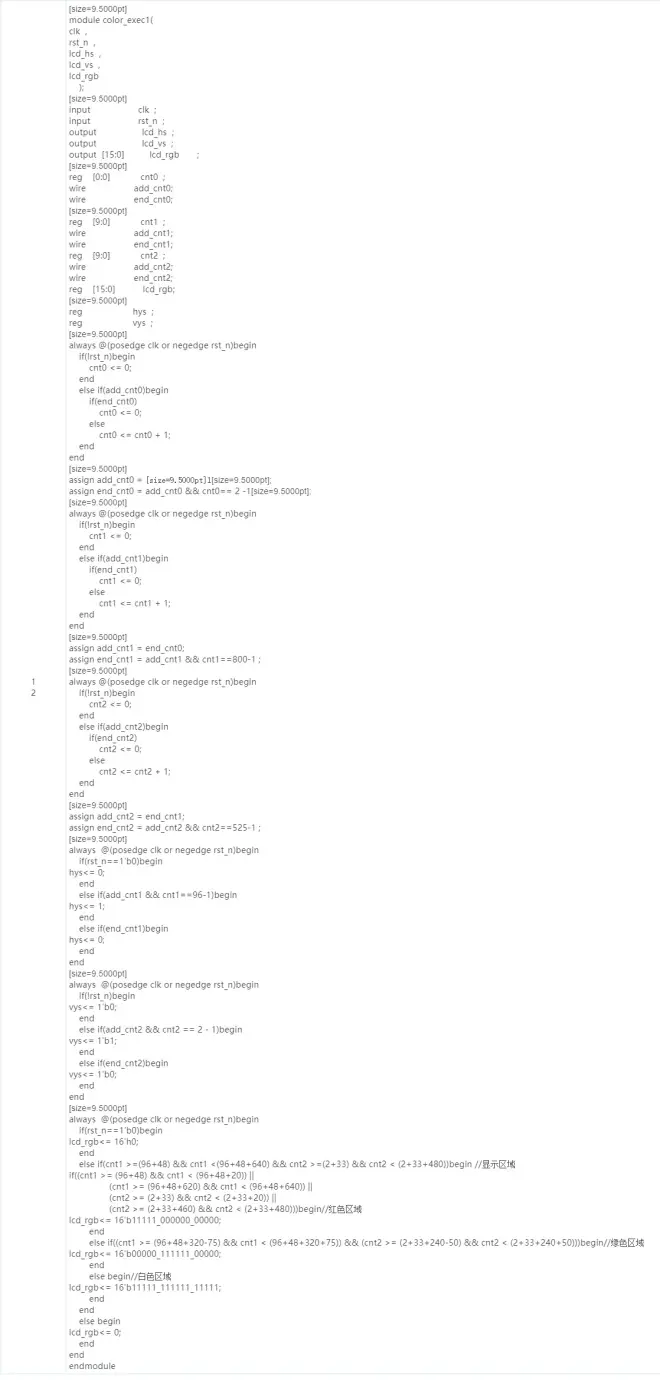

至此,整个代码的设计工作已经完成。最终得到完整的设计代码如下:

下一步是新建工程和上板查看现象。

5.2 综合与上板5.2.1 新建工程

打开软件Quartus Ⅱ,点击“File”下拉列表中的New Project Wzard...新建工程选项。

图3.9-11Quartus新建工程

直接点击“Next”。

图3.9-12Quartus新建工程介绍

此时出现的是工程文件夹、工程名、顶层模块名设置界面(目录为:D:/mdy_book/rec_exec1,工程名和顶层名为rec_exec1),完成设置后点击“Next”。

图3.9-13 QUARTUS新建工程设置名称

选择“Empty project”后点击“Next”。

图3.9-14 QUARTUS新建工程类型

点击右侧的“Add”按钮,选择“color_exec1.v”文件后点击“Next”,完成文件添加。

图3.9-15 QUARTUS添加文件

对芯片型号进行选择,在“Device family”选项中选择“Cyclone ⅣE”,“Available devices”选项中选择“EP4CE15F23C8”,随后点击“Next”。

图3.9-16 QUARTUS选择芯片型号

直接点击“Next”。

图3.9-17 QUARTUS设置工具界面

点击“Finish”,完成新建工程。

图3.9-18 QUARTUS新建工程汇总界面

5.2.2 综合

新建工程后界面如下图所示,点击“编译”。

图3.9-19 QUARTUS新建工程后界面

编译成功如下图所示。

图3.9-20 QUARTUS编译后界面

5.2.3 配置管脚

进行管脚配置,在菜单栏中点击“Assignments”后点击“Pin Planner”,此时会弹出配置管脚的窗口。

图3.9-21 QUARTUS配置管脚选项

在配置窗口“location”根据信号和管脚关系配置管脚,配置完成关闭“Pin Planner”即可自动保存配置信息。

图3.9-22 QUARTUS配置管脚

5.2.4 再次综合

再次打开“QUARTUS”软件,在菜单栏中选择“Processing”,随后点击“Start Compilation”再次进行综合。

图3.9-23 QUARTUS编译选项

出现 QUARTUS 编译成功标志时表示此次编译成功。

图3.9-24 QUARTUS编译成功标志

5.2.5 连接开发板

下载器接入电脑 USB 接口,将开发板接上电源,开发板的VGA口连接到一台显示器上后按下蓝色开关。

图3.9-25开发板连接图

5.2.6 上板

打开 QUARTUS 界面后单击“

”图标:

图3.9-26 QUARTUS界面

点击“add file”,添加.sof文件,完成添加后点击“Start”,在“Progress”中会显示进度,当进度条显示“100%”为成功,可观察显示器现象。如果此时开发板连接的显示器显示出了设计目标中需要的画面则代表设计成功。

图3.9-27 QUARTUS下载程序界面

第6节 扩展练习

至此,VGA显示矩阵设计已经完成,相信同学们已经可以完全掌握这一设计。那么在掌握这项工程后可以多做一些思考,尝试在工程原理不变的基础上进行一定的数据调整,试着改变图像显示区域或者改变显示颜色等参数,挑战一下独立完成多个设计。也欢迎有更多思路和想法的同学前往至简设计法论坛上进行交流讨论。