为什么说龙芯圈只会看IPC是单核时代的思想?谈能效的重要性

额……老铁们,我图吧老捡垃圾的了。今天咱简单接着谈下图吧捡垃圾理论建设的日常,之为什么现在只会看IPC是单核时代的思想以及能效比的重要性。

主要论证本文内容的原因依旧是龙芯圈在咱面前孜孜不倦反复强调所谓的同频性能或者说单核性能,而忽略真正重要的参数比如芯片本身的能效比以及功耗表现。至于兼容性这种高深的概念我想现在连MIPS都不能兼容的龙芯咱还真不指望龙芯圈他们能理解。

前作:图吧小白教程 篇一百三十九:为何评判现代CPU的水平不能只看IPC?论能效比在多核时代的重要性

揭秘龙芯圈如何攻击国产芯片03:以IPC代表性能提升

这期咱不想多说太多关于国产芯片本身的事,只是希望各位能理解所谓的单核或者同频性能的概念早就在二十年前左右就过时了就行。大概是在AMD在2005年4月21日,发布了他们的第一个双核处理器双核速龙™64是由AMD设计的桌面级64位处理器。处理器内置了两颗速龙™64核心,两个核心通过System Request Queue连通。首批产品使用90纳米SOI工艺生产,之后亦推出使用65纳米工艺生产 这个时候IPC就已经没那么重要甚至没什么用处了。因为不用多长时间,下代产品就已经开始堆四核甚至下下代直接出六核了。AMD是在AM3没+的45nm时代完成的堆原生六核,而英特尔在X58时代开始堆核并引入智能睿频(主要是区分全核睿频)技术,距今十五年前改变了多核处理不如高频双核处理器的观点,在32nm时代完成堆原生六核。89后期图吧标配的X79 X99根据E5的版本不同也都是分别原生六核八核甚至十核十八核二十二核,这些产品至今依然是图吧主流,因此所谓的单核性能论同频性能(即所谓的IPC)论在图吧是没什么用的。

这里我们简单把时间调到三十年前,看下早先的单核CPU产品当时的同频性能之争,大概就能明白一味的追求同频性能的问题在哪了。

和英特尔只追求频率不看同频性能相反,当时的X86友商其实有相当大胆先进的设计,包括今天我们熟知的APU或者说SOC设计,至于单核时代非常重要的同频性能和其实友商也没有放下,但是结果就是倒在了能效比上。

亜恵恵阿由:从Cyrix到VIA,捯一捯兆芯的前辈们(上)

Cyrix创始于1988年,最初是制造兼容80387的协处理器的,后来开始制造兼容486的中央处理器。之后,Cyrix尝试制作可在同一个时钟周期同时执行2条指令的下一代处理器,以求大幅度提升性能,代号M1。然而由于开发困难,先行将只能执行1条指令的M1架构的分支产品M1SC拿到市场,称为Cx5x86。

说起来,Cx5x86我好像还是见过一次的。记得是在初中一同学家,他给大家炫耀几秒就能赢一场星际。嘛,其实就是输入直接获胜的秘笈。有多卡不记得了,只记得退出的时候会死机,只能直接关机。大概只是内存太少的原因。不过我也不知道为什么我会认为那台机器是Cx5x86,也许是混乱的错误记忆。 Cx5x86的销量不错,使得Cyrix可以继续M1的开发。1995年10月推出了80MHz的「6x86 PR90」,命名中的PR全称是Pentium Rate,意味着性能相当于Intel的Pentium 90MHz,跟后来大家都很熟悉的AMD Athlon XP的「几千+」的命名如出一辙。

这个AMD速龙几千+等于英特尔某CPU同频的命名法其实咱家以前用的CPU也有,比如这款:【图吧日常】50包邮的闪龙2800+754板U测评

这个1.6G的闪龙单核90nmCPU的命名2800+就是表示它相当于英特尔P4 2.8G的性能,当然今天看来实际上性能也就是不到图拉丁P3 1.0G的二倍(1.9),同频性能略好于图拉丁奔腾3而已。如果英特尔当年下放以色列海法小组负责的从图拉丁P3(P6架构)改进的PM奔腾M到桌面U的话其实同频性能应该是和AMD K8相当的。

而这个耍猴或者说反耍猴命名法其实最早不是AMD在用,而是Cyrix。

6x86之后又发布了100MHz(PR120)、133MHz(PR166)、150MHz(PR200)的型号。 从命名和实际频率可以看出,6x86的同频性能是强于Intel Pentium的。最高频的6x86 PR200耗电量过高,达到24.6W(现在来看似乎不算什么,但当时Pentium只有15W),因此Cyrix在IBM的制造工艺提升的同时多次降低了电压。当时IBM的制程是0.5μm→0.35μm,电压3.52V→2.8V→2.45V。2.8V版本称为6x86L,最大耗电17.1W;最终的0.35μm制程2.45V电压的版本称为6x86LV,最大耗电13.2W。功耗问题控制下来了,但因为耽误了不少时间,给之后留下了隐患。 6x86的整數性能优异,命名中的PR,就是以整数性能相当于Pentium的对应型号由来的。但是浮点性能甚至不如i486。理由是当时的应用基本是使用整数计算,所以Cyrix将更多的资源放在整数上。还有一点,6x86与Pentium的指令集并非完全兼容。一部分使用了Pentium独有指令的软件,为6x86推出补丁用以解决问题。

指令集并非完全兼容这个情况其实在AMD后期的产品中同样出现过,SSE4和SSE4A的区别就是SSE4A去除Intel的SSE4其中对I64优化的指令,导致一些只支持SSE4的程序无法使用SSE4A,但是可以通过补丁实现调用SSE4A。

后期AMD在发布SSE5之前就决定兼容SSE4和AVX而不是继续另起炉灶,这也算是一种妥协。

接下来,1997年,Cyrix发布了核心代号为M2的「6x86MX」,与前面的6x86最大的区别是内置了MMX指令集。频率从133MHz(PR166)到233MHz(PR266)。最终版本发行时间为1998年2月。最初版到最终版相隔一年的原因还是制程的改进。Cyrix是无晶圆厂芯片设计公司,制造交由三家完成,分别为IBM、SGS汤姆逊(现意法半导体)、美国国家半导体(NS),三家的制造工艺不同,最终出货时频率和耗电也不尽相同,弄得很麻烦。

同样的处理器使用不同的工艺导致不同的能效表现至今看来依然是很麻烦的事,这种抽奖式的产品体验最近发生在iPhone6S时代的苹果A9处理器——分别使用了三星14nm和台积电16nm,结果14nm被16nm吊打,无论功耗性能续航都毫无还手之力,换言之,三星工艺的A9能效不如台积电工艺的A9,然而苹果宣称两者没有区别,所以对于消费者来说只能自求多福。

这种相比三星为代表的储存企业涨价导致用不起UFS只能和EMMC混用还不一样,这种自研CPU的代工完全是可以选择的,苹果在当年甚至用得起NVME但是不愿意像A8或者A10一样为CPU或者说SOC产品采用统一的工艺这个是没什么借口的。所以可想而知当时对于Cyrix来说不同工艺版本的处理器产品会带来多大的问题,不患寡而患不均就是这样的道理,除非公开降同样设计产品的不同工艺版本从定价上拉开档次,那就相当于承认某一家的工艺处于劣势,这代工厂恐怕也不是一个无晶圆厂芯片设计公司能得罪得起的。

随着制程的进步,6x86MX进一步将频率提升至300MHz(PR433),同时更名为「Cyrix MII」,以表示竞争对手为Pentium II。但由于前面因代工和耗电问题耽误了时间,投入市场较晚,此时Intel的P6(Pentium Pro、Pentium II)和AMD的K6在整数性能上已经追上Cyrix,Cyrix在浮点性能上本来就不敌前两者,此时Cyrix MII已经失去了竞争力。

虽然同时选择不同代工厂给Cyrix带来的麻烦加上浪费的时间后果很严重,最后真正压倒Cyrix的还是其只注重整数性能而浮点性能瘸腿餐费,这样实际的性能差距无论在命名和宣传上怎么耍猴都是没法掩盖的。因此消费者自然会选择用钱投票。顺带说下现在的龙芯在性能宣传上也有这样的趋势,暴芯这种产品的出现完全是因为现有国产芯片的实际性能达不到英特尔i3-10105的性能水平,这个没什么可说的,没有就是没有,兆芯的KX6000八核也不过是个区区I5 7400的水平,性能雀食已经不够看打不过暴芯的10105了也得承认。

别看曾经有过得看现在在产的有什么,毕竟不能指望麒麟710A打10代I3,海光也是一样的道理,理论上通过改进是有相比ZEN1提升15%IPC30%整体性能的水平,但是实际上在实体清单不能大规模量产也是真的,这就和鲲鹏930或者麒麟9010一样属于纸面上的东西只存在于设计图了。龙芯同理,而龙芯甚至实际性能在下代产品即使能量产也不能和i3-10105抗衡这个也是真的,不考虑不同架构跑模拟的损失也打不过,所以宣称没发售的的下代产品性能和10代酷睿相当(很可能是i3-10110U)没有意义。只会给人有这种感觉:

用事实说话什么时候拿出产品在市场上真和英特尔10代U过过招让暴芯这种东西不再出现才是真的。

Cyrix计划之后计划推出整合图形(2D/3D)机能、内存控制器、共享二级缓存的SoC「Cayenne」,支持双通道Direct RDRAM的高速CPU「Jalapeno」,以及再之后称为「Serrano」的细节不明的代号。资料说在1998年10月的MicroProcessor论坛上是如此公开了路线规划的。笔者查到了97年的MicroProcessor论坛,当时已经发布了「Cayenne」的架构了。・Cayenne(意为红辣椒),将有15个新的多媒体指令,重点放在2D图形、DVD、3D图形处理上。2个浮点单元、2个MMX处理单元、64KB的1级缓存。 ・Cayenne可在1个周期处理4个浮点运算与2个MMX指令。可以实现峰值1GFLOP以上的浮点运算能力(约为Tualatin Pentium III 1.4GHz的一半),达到5倍于Pentium II 的3D性能。 ・Soc MXi将整合Cayenne处理器、SDRAM控制器、AGP控制器、DVD解码等功能。内存带宽达到2GB/秒、AGP能力达到Pentium II的2倍。MXi将以0.25μm生产,die面积为90平方毫米。该Soc将于98年第2季度生产相当于PR300~400的产品...

之所以能画这么大的饼,是因为1997年3月,Cyrix被NS收购了,成为了NS的子公司。通过收购,Cyrix不愁钱了,而且也可以更好地利用NS的晶圆厂,NS的晶圆厂利用率高了,型號可以画得更细等等,各种好处。 98年发布了Cayenne之后,也确实在开发了。Cayenne的设定是兼容Socket370,内置2级缓存的,将使用0.18μm生产,定名Gobi,准备99年年中推出。于是到了99年年中,嗯,NS把Cyrix卖给了VIA。VIA收购Cyrix后,上面说的已经基本开发得差不多了的Gobi,改名Joshua,于2000年2月,差一点儿就上市。据http://ascii.jp的文章作者讲,当时测试样品都到媒体手里了,测试也跑了,然而最终并没有发售。 但是市面上有Cyrix III啊。那是因为,VIA在收购了Cyrix之后没俩月,又收了一家x86处理器公司。后来以Cyrix III为名发售的处理器,里面其实是这家后收的公司的。Cyrix Gobi的CPU设计,完全没有被使用。

现在Cyrix唯一的技术遗产,是延续M1架构的面向机顶盒等嵌入式设备的微处理器——Geode,是AMD的。在NS收购了Cyrix之后,Cyrix的嵌入式微处理器部分归NS所有。在99年将Cyrix卖给VIA时,并没有将嵌入式这一部分一并卖给VIA,而是在2003年把嵌入式这一部分卖给了AMD。 到这里,Cyrix的事儿已经完了。前面说到VIA的Cyrix III只是一个名字,其核心来自于VIA收购的另一家x86处理器公司。这家公司叫Centaur,被收购前的产品系列叫WinChip

后来的事就都知道了,Cyrix被VIA高价收购之后设计成果被弃用,团队被解散,只剩下了部分技术专利和资料,虽然VIA后来还是有X86的设计能力但是实际上是来自IDT WINCHIP的Centaur团队了,这家收购价比较便宜只有Cyrix的大概六分之一。而IDT WINCHIP的设计原理以及取舍则是另外一回事了

Cyrix从人们视野中消失之前,虽然小众,也是挺有存在感的。Core2时期VIA还有C7在卖,而联想到C3,这C7的C显然是延续自Cyrix。然而万万没想到VIA时代的Cyrix只剩下了一个名字(后来就只剩下一个字母了),真正的核心技术是继承自一个笔者此前从未听说过的Centaur WinChip。

Centaur是IDT(Integrated Device Technology, Inc.,现已被瑞萨收购)的子公司,设计x86处理器。CEO是曾在IBM设计大型机System/360的Glenn Henry。Centaur设计开发采用顺序执行、单管线精简指令集(RISC)的CPU,致力于低能耗的x86兼容实现。CPU并不直接执行x86指令,而是将x86指令集转换成精简指令集后执行。实际上这种做法在Intel Pentium Pro和AMD K6上已经广泛使用,但Intel和AMD采用的是乱序执行管线,很适用于高性能地执行拆分后的精简指令。而Centaur选择精简指令集的理由是精简指令集适宜实现低耗电。

这里需要插一部分关于半人马的设计理念的资料,简单给各位看下:

国产处理器拾遗:超级抠门的Centaur造就了威盛x86……但他本人后来兴趣转向于「将RISC 的精神,引入高度普及的x86 指令集相容处理器」,而IBM 高层对此并不感兴趣,所以他在1988 年离开了任职21 年的IBM,转战Dell ,成为该公司历史上第一位研发部门副总裁,并在1993 年升任管理产品线的资深副总裁。 那时Glenn Henry 注意到一个问题:他无法在市面上买到售价低于160 美元的个人电脑处理器,这也变成降低个人电脑零售价格的最大障碍。如果没经历过1990年代初期,各位可能很难想像那时的x86 处理器有多昂贵:在1994年第一季,连486DX2 66MHz 都要440 美元,更不用讲793 美元的Pentium 60MHz 了。 有鉴于此,Glenn Henry 在1994 年离开Dell,重操旧业,投入于x86 指令集相容处理器的研究。有趣的是,当时在MIPS 工作的某位「前IBM 人」Tom Whiteside,希望Glenn Henry 可打造出同时兼容于MIPS 与x86 指令集的处理器,将MIPS 推入个人电脑市场,这也是Centaur 此名的由来:半人半马。令人难以置信的超低研发费用与超短开发时程 不过他们拿着这个混合式处理器架构的提案,绕了众多研发MIPS指令集兼容处理器的厂商们(那时很多人做MIPS)一大圈后,最后只剩下一间公司愿意买单:IDT,然后Centaur 就在1995年成立了。但Glenn Henry 和他的老板IDT CEO Len Perham,很快的承认残酷的现实:MIPS 没有机会进入个人电脑市场,专注于x86 会更有价值,Centaur 就开始以极度拮据的预算,在x86 处理器踏出了第一步,因为以MIPS 兼容处理器和SRAM 做为主要业务的IDT,并不是什么有钱的大公司,支付不起像Intel 和AMD 那样巨大的研发团队。 Glenn 只能采取精兵政策,从摆明放弃研制x86 处理器的IBM 和TI,挖来对x86 有经验的工程师,在德州奥斯丁的Somerset PowerPC 研发中心弄来PowerPC 工程师,并从前东家Dell 找来个人电脑专家,组成了大约40 人的研发团队。 接着奇迹就降临了:Centaur 仅用不到一年的时间,就Tape Out初代的C6 处理器(第一代WinChip)设计,并在1996 年7月,首次Windows 操作系统开机成功。更骇人听闻的是,研发经费仅1,000 万到1,500 万美元,很可能连Intel P6(Pentium Pro)的十分之一都没有。

开发成本缩减至此,就算Centaur 只吃下1% 的x86 处理器市场占有率,都足以养肥自己了。况且这笔钱还有一半是由日本的MIPS 处理器厂商NKK 所分担的,他们在当时被当作IDT 部分产品的替代来源。 Centaur 如何打造如此夸张的世界奇观?在AMD 的K5 创造者Mike Johnson 口中「毫无道理可循」的x86 指令集不是出了名的难搞吗?这就跟他们坚守的三原则:简单(Simple)、迅速(Fast)、便宜(Cheap)密不可分了。 成本至上,扬弃超标量流水线和动态分支预测 1990 年代初期,「一个指令跑不够,你可以执行两个」的超标量处理器(Superscalar)流水线,与「以古鉴今」预测分支是否发生、确保指令流水线不会停摆的动态分支预测(Dynamic Branch Prediction),是奠定高效能处理器的重要技术指标,也激增了处理器的结构复杂度。

信奉精简教条的Glenn Henry 却不吃这套,吃了砰陀铁了心,要用最短的时间、最低的成本,做出最便宜的产品,所有的晶体管预算都要砸在刀口上,不允许任何一丝一毫的赘肉。 就这点来看,Centaur 的理念,和同时期的Rise 与同年成立的Transmeta,完全如出一辙,并不打算跟Intel 硬拼,而是希望在低价电脑和笔电市场开拓一片全新的蓝海。唯一的差别只有Rise认清时势急流勇退,Transmeta 如同蜡炬般的烧尽资金,资源消耗最少的Centaur 却依旧幸存至今。 Centaur 扬弃超标量流水线的主因很简单:有效率的超标量流水线,须搭配大量的配套措施(像可让指令解码器同时撷取两个指令的双通道指令Cache),太过复杂,迟至2000年揭露的C5X,才算迈进超标量流水线的世界,只是C5X 也因成本因素,默默的不见,直到2008 年的Nano(CN)才重现曙光。

关于不做动态分支预测,就是纯粹的精算了,Centaur 预估在C6 引进类似Intel Pentium 的动态分支预测功能,会提升5% 效能,但将明显增大芯片面积,得不偿失。 Centaur 将极为有限的资源,集中在认定的效能瓶颈,如便于提高主频速率、集中加速最经常被执行简单指令的微指令转译,用较高容量的Cache、位址转译后备缓冲区(Translation Lookaside Buffer,TLB)和分页表目录Cache(Page Directory Cache,PDC),设法弥补缺少超标量流水线和动态分支预测的不足。所有的努力,仅局限于一款「最高效益的表露处理器」。 也难怪微处理器报导(MicroprocessorReport)主编曾戏称:Centaur 做的不是「超标量(Superscalar)」,而是「超级标量(Super “Scalar”)」处理器。

长话短说,相比Cyrix的正面硬刚仅差一定的浮点性能其余和IA打得有来有回,Centaur和RISE以及全美达(Transmeta)走的都是低功耗低成本低价位的低端路线,致力于降低PC的整体成本和功耗(也可以认为是使用成本,低功耗往往需要高能效比,而能效比则是决定同样性能需要消费的电能之关键参数)

当初Centaur的原计划是造出同时兼容于MIPS 与x86 指令集的处理器,将MIPS 推入个人电脑市场,这也是Centaur 此名的由来:半人半马。但Glenn Henry 和他的老板IDT CEO Len Perham,很快的承认残酷的现实:MIPS 没有机会进入个人电脑市场,专注于x86 会更有价值。

Centaur设计的IDT WINCHIP CPU并不直接执行x86指令,而是将x86指令集转换成精简指令集后执行。其实这点X86阵营都差不多,Intel和AMD也都是将x86指令集转换成内部微指令⑴再执行的,RISC和CISC早就没那么明显的界限了。

⑴大多数现代 x86处理器并不直接执行 x86指令 ,而是先将每条 x86指令转换 为若干条与 load2store R ISC指令类似的微指令 (Micro Instructions, uins) ,有的也称作微操作 (Micro Operations, uops)。简单 x86指令一般转换为一条微指令 ,而复杂 x86指令一般转换为若干条微指令构成的微程序 (Micro Program)。相对于直接执行x86指 令 ,微指令可以更加容易采用乱序执行等先进体系结构技术——x86指令集兼容处理器中微指令的设计与验证

所以全美达的失败只能看作是当时的VLIW相比X86的P6架构运行X86程序并没有非常高的性能或者说能效优势,而后来的安腾IA64彻底失败则表示没有生态的架构或者说指令系统(ISA)雀食没有前途,即使定位服务器市场也是好歹需要有人维护生态的,Centaur创始人当年的眼光也是对的,MIPS没有进入PC市场的机会,如今过去了三十多年VLIW的安腾早已作古,而MIPS的实际继承人龙芯也依然在PC市场被X86 ARM杀得找不到北,这就是现实。

Centaur于1997年10月发布了「WinChip C6」。采用IDT的0.35μm工艺制造,首先推出了180/200MHz的产品。转年的1998年4月,推出了225/240MHz的型号。频率最高的240MHz型号仅有11W~13W的低耗电,但整数性能平平,且因为FPU跑在半速上,浮点性能也绝对谈不上高。 接下来推出的「C6+」,改善了劣势的FPU部分,跑在了全速上,同时加入了MMX/3DNow!单元。改进制程,提高频率,最终实现了在频率提高到250MHz的同时,耗电维持不变。

改进后的「C6+」,以「WinChip 2」和「WinChip 2A」的名称发售。其中WinChip 2是0.35μm制程,WinChip 2A是0.25μm。WinChip 2于1998年9月发售,WinChip 2A为1999年3月。 watch.impress真是个神奇的网站,现在还可以找到当年的评测。可以看到半速FPU的C6浮点性能之差、更新为全速后C6+(WinChip 2)浮点性能的提升,以及整体上与同期CPU性能上的对比。

https://pc.watch.impress.co.jp/docs/article/990618/hotrev15.htmpc.watch.impress.co.jp/docs/article/990618/hotrev15.htm

接下来Centaur的路线是阶段性地改良。首先是代号为「W2B」(产品名为「WinChip 2B」)的,将核心与I/O中的电源平面分离出来,通过降低核心电压,以达到降低耗电的目的。接下来代号「W3」(产品名「WinChip 3」)的产品,将1级指令缓存和1级数据缓存各增加至64KB,以改善性能。 继续下去的话,「W4」预计是改进管线构造(一部分已经进入开发阶段),然而此时陷入了与Cyrix同样的状况。母公司IDT于1999年7月决定退出x86兼容CPU市场。即使包含x86资产的买家尚未确定,也要退出。次月,公布VIA收购包含Centaur在内的WinChip相关资产。至此,VIA Technologies拥有了两个CPU核心与设计子公司。VIA

在接手了两家x86资产的次年, 2000年6月,VIA发售了核心代号为「Samuel 1」的产品,品名为「CyrixIII」,对应Socket 370接口,台积电生产。

前篇说了,这颗名为「CyrixIII」并不是延续Cyrix的架构,而是Centaur。VIA CyrixIII是基于Centaur出售时正在开发的「W4」核心。最大的原因在于,Cyrix下一代的方案与VIA的经营范围出了冲突。看过上一篇的读者应该有印象: Cyrix计划之后计划推出整合图形(2D/3D)机能、内存控制器、共享二级缓存的SoC「Cayenne」,支持双通道Direct RDRAM的高速CPU「Jalapeno」……

虽然这些直到初代Core i3才被Intel做出来的超前设计值得惊叹,但对于VIA来说,继续这个路线就相当于放弃了对Intel和AMD两家提供北桥,至少也是要占用现行对I/A设计北桥的精力。虽然很快大家的北桥就不通用了,但在当时还是一块北桥大家都能用的情形,VIA也不知道。所以VIA放缓了Cyrix路线的开发。但其实本来只是放缓。 在VIA本来预想的路线图中,是想要同时发展Cyrix和Centaur两路线的。Cyrix面向桌面,与Celeron和Duron竞争低端市场,Centaur则是利用它的低功耗,面向嵌入式机器。

在这条预想中,即使利用Cyrix的核心遗产进行开发,其实也不会走CPU内置北桥的设计。一是当时的die尺寸这么做不现实(10年后的初代Core i3也还是从胶水开始呢),另外一点,在Cyrix于Intel你来我往的诉讼中,Cyrix是带着总线专利一起卖给VIA的,做成分离的,一个北桥同时兼容VIA自家的CPU与Pentium III,共用Socket 370接口,对于VIA来说怎么想都是更合算的。不过最后,VIA还是没有再开Cyrix的核心路线,而是挂Cyrix的皮,把Centaur路线的后续产品放了进去。 之所以用Cyrix的皮,是因为当时Cyrix还是有一定市场占有的。但是因为Cyrix MII时代的高耗电低效能,反而这个名字带来了反作用,给人了低端的印象。后来的产品就改叫C3了(虽然C的来源这么看还是Cyrix的C,但是已经「去Cyrix化」了)。

说回VIA这颗名为「CyrixIII」的CPU。1级指令缓存和数据缓存各64KB,与W3相同,但依然没有加入2级缓存(两年前的Celeron 300A已经有2级缓存了),频率也仅为533~677MHz,因此性能低下是必然的。但最大耗电19.3W与低发热也算是成功的地方。自此,VIA带着Centaur的核心遗产,Cyrix的总线官司换来的x86授权,开始了低功耗x86 CPU的道路。

顺带说下,上图提到了SIS GPU,当年的SIS也有生产X86 CPU的能力,不过只有32位,他们没有AMD64的授权无法支持64位CPU产品的设计。好在AMD64的专利过期也就不过今年的事了。也就是说AMD发布64位处理器已经有20年的历史了。如果现在某地实现大批量生产速龙64处理器理论上是不需要缴纳专利费的。现在上图中的VIA C3各位可以看见因为不支持SSE指令集所以即使运行XP也没多少可执行的软件只能停留在博物馆收藏了,而VIA C7则好得多。虽然性能依然感人,但是它大概率是可以在XP环境下接着用到报废的:

它虽然不支持64位,但是却有XP下需要的所有指令集,SSE SSE2 SSE3,没问题。所以今天买一台HP的C7M的笔记本依然可以装个火狐上网看视频(虽然GPU不支持H264硬解)或者跑个MSTSC当上位机都好歹是个东西,而同年代的POWERPC IBOOK G4却连上网听音乐都是个奢望了,没有浏览器支持现在的网页!在转X86之前的苹果机现在整个机器就是个大手办,没有一点使用价值。 IBM/摩托罗拉/苹果的PowerPC今天连开源都没人愿意用了。生态是第一位的,然后是性能达到基本的合格线,再往后就是能效了。

能效比到底多重要?简单来说,相比单核时代的IPC同频性能决定单核CPU在存在物理频率上限下最高性能的思路,能效比则是决定在有限的功耗和散热下能实现的性能之关键。

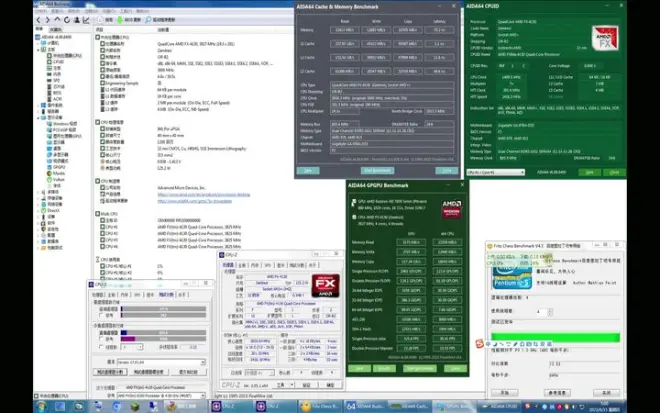

咱还是和上期一样拿ATOM举例,看图

ATOM N4100这个U就非常有代表性,6W TDP,4W SDP,功耗可解锁到10-15W,解锁完功耗性能基本和J4125水平差不多,单跑CPU正常功耗是10W左右。整机功耗很低,可以用12V2-3A电源供电,给5-10A都是非常有富余的水平了。就这么一个U,全核2.3G,象棋跑分约为10.4倍,CPUz不到750分,貌似随便找个老年头的CPU同频性能(即所谓的IPC)都比它强。

比如AMD X4 600E,2.2G全核象棋跑分轻易达到了四核10.5倍以上, 45nm的工艺,TDP42.8W。CPUz没法看因为K10.5缺SSE4所以得分偏低,单纯比拼算力的象棋还是没问题的。所以说K10.5相比ATOM GEMINILAKE的同频性能略强,但是功耗上差距就很高了,相差至少四倍,也就是说即使是同为低功耗产品的X4 600E时隔多年依然无法在能效上和ATOM竞争。反倒是45nm时代的英特尔在能效上强得多,虽然有FSB小水管总线和胶水核心,但是他们的P系列笔记本标压低功耗U依然可以在25W的功耗下拿下相当不错的跑分性能(象棋跑分7倍左右),甚至到今天也是能用的水平。台式机当时有E5200和E5300这种怪物,风冷轻松3ghz,同频性能未见得比AMD强多少但是能效比高就可以在堆不起核(775胶水四核效率不高)的情况下轻松拉起频率。

咱要正视这个差距,现在国产即使是用了TSMC的16nm工艺依然在能效上只能和英特尔14nm时代的ATOM或者说赛扬银牌勉强打平。龙芯圈经常贬低的兆芯19年的产品KX6000系列的CPUz的单核跑分也就180左右,但是受益于原生八核的规格所以整体性能得以和I5 7400相当,象棋跑分21倍左右,八核产品在2.5G的频率下TDP 50W,四核2.2-2.6G 25W,CPU跑分和N4100相当GPU相比UHD600甚至还差一些。这就是现实的差距。

好在兆芯KX6000并不是陆家嘴小核心的终点,KX6000G在加强了GPU 4倍性能的同时还改进了核心的设计在同样的16nm工艺下功耗可低至15W(可解锁)频率高达3.0G(15W,3.3G@25-35W),也算是在能效上再接再厉吧。希望国产能在低功耗X86核心上继续研发,填补市场的空白(英特尔大小核放弃了原ATOM精简小核心架构复杂化核心设计延长流水线快速提高频率提升整体性能却忽视了能效,AMD根本没有小核心设计低功耗产品只能从大核心精简降频类似当初的CORE M)。

那么高能效的小核心有什么用呢?简单来说就是在同样的功耗下可以塞进更多的核心实现整体性能的快速增长,兆芯17年开始就下放八核产品至民用级个人用户就很容易堆出相当庞大数量的核心弥补单核性能的不足,而英特尔显然版本比较落后,到了大小核时代也就是今年才想起来给八核小核心产品放出来然而售价却异常感人还砍了不少东西比如单通道内存,但还是四舍五入换来了性能的倍增。

那么既然堆核能快速提升性能为什么不直接堆大核心?

不是不想而是不能,至强就是极限了。环形总线是有极限的,X79的时代环形总线最高是10核,再多了就需要一个CPU内有好几个环形总线分别连接一部分核心了。这方面其实还是AMD比较内行,CCD与IOD分立内部CCX使用交叉开关互联,外部CCD之间、CCD和IOD使用IF总线互联。总而言之AMD更容易堆出更多的核心,AMD的RYZEN核心其实更像是介于英特尔大核心和小核心之间的中核心。而大核心就没这么简单了。

环形总线也好或者其他总线也好小核心是可以四核为一簇的,这样就能很容易解决大核心的核心数量上限问题。

目前的现状就是英特尔根本就不敢把ATOM纯小核心堆出来大量核心的产品下放到个人电脑级用户,这样会显得现在的大核心能效非常拉跨没人愿意买大核心产品,难道你更愿意为了性能用功耗上百瓦甚至千瓦核心功率密度高于反应堆的产品吗?还是性能够用功耗合理而且良品率高价格便宜的小核心产品,相信这点各位都有答案。

其实AMD现在已经意识到了这点,所以他们的产品早在APU以前的推土机时代就已经开始打磨架构提高能效比。论同频性能8350比8150要好一些,大约强5%-10%之间,后来的压路机挖掘机同频性能也差不多,但是功耗就好了很多。

同样的2M4T从FX4130时代的125W+降到了A8 7680的最低45W,这期间只是把工艺从格罗方德的32nm换成了28nm,不得不说如果后期的挖掘机时代AMD愿意出4M8T的产品甚至APU产品那就不会出现性能被英特尔吊打功耗直接翻车的情况了,要知道AMD的4M8T推土机打桩机CPU在一些供电不好比如咱手上这张CPU供电只有4PIN的970主板上是直接点不亮或者进不了系统的(进系统界面卡死),这表示带动功耗很高的CPU不仅需要电源散热要好,甚至还需要主板供电也必须有一定的规格,这对于消费者来说就非常难受了。现在的英特尔大核心的功耗比当年的推土机只多不少,可想而知用起来会多难受。

功耗问题是可以通过打磨架构改进物理设计更换工艺解决的,而频率和同频性能通常来说一般认为和流水线长度有关,流水线长度越长提频更容易而IPC或者说执行效率就越低,反之缩短流水线就更容易提升同频性能也就是所谓的IPC但是通常拉高频就比较困难。还有就是和核心大小有关,大核心设计复杂本身同频性能就更容易提高但是能效往往更低,小核心设计精简同频性能往往更低但是更节能更省电能效更高且更容易堆核。

所以所有的设计都是一种取舍,不能单从一种或者两种参数就评判芯片设计的水平。还是那句话,IPC代表不了芯片设计水平,甚至代表不了芯片本身性能,这点老外的架构分析网站在测评的时候看得很明白。

The terms “architectural efficiency” or “performance at the same clock” are sometimes taken as metrics of goodness in and of themselves. Perhaps this is one way of apologizing for low clock rates or a way to imply higher performance when the microrachitecture “someday” reaches a clock rate that is in fact unobtainable for that design…

David B. Papworth, Tuning the Pentium Pro Microarchitecture, IEEE Micro

所以龙芯圈在听了咱前作的论断之后也选择了采纳,开始攻击起兆芯和其他国产芯片的功耗了。遗憾的是他们的目的指向性太强甚至出现了明显不符合现实的结果这就很有意思了

兆芯KX-U6780A从开机到烤机(主板/CPU/内存/硬盘/核显/风扇) BV1fX4y1X7rn

甚至出现了龙芯圈全程对龙芯吧小吧主的视频进行录屏改个标题接着发的套娃操作:

兆芯kx6780从开机到烤机 功耗感人似火炉 轻松爬上100多瓦 兆芯单核性能更是拉拉胯 龙芯是兆芯的单核性能近2倍 龙芯功耗18到35瓦 BV1q24y1J79e

所以标题的明显错误手册显示龙芯3A5000实际功耗最高可达55W就先不提了,咱自己测兆芯KX6780A的功耗结果在此各位请自行查阅:href="https://www.bilibili.com/video/BV1aM4y1Z7mW/";>【闲话兆芯番外04】龙芯圈宣称6780A功耗100W?真实烤机功率测试 BV1aM4y1Z7mW

我想这种操作只会让更多人看清龙芯圈对其他国产芯片的测评是存在蓄意贬低或者攻击的目的的这样就够了。所以说对付他们都说了非常容易,只要把他们自己做的事拿出来看就很容易看明白怎么回事了甚至不需要咱对龙芯本身进行过多指摘。龙芯什么水平自然不会像龙芯圈吹的那么NB,兆芯什么水平因为兆芯本身售价比龙芯便宜好几倍所以各位垃圾佬很容易买一台回去自己试下看看情况也不用咱多说,总而言之龙芯圈对其他国产芯片重拳出击尽显武德只会让更多人对龙芯圈敬而远之并且对其他国产芯片产生兴趣。

据说龙芯吧小吧主自己也承认了自己那个兆芯烤机120多W的视频是依靠USB设备提高了整机功耗实现的,不过咱没看到截图。咱只知道无论咱自己怎么烤机这台KX-U6780A的整机功耗都达不到100W,实际CPU拉满载的工况下整机功耗也就70W,符合TDP,降频到2.4G还能把整机功耗降到40-50W,这才是KX6000真正的问题,最佳性能-功耗(能效)平衡点在全核2.5G,然而兆芯大量出货的八核产品普遍定2.7G的主频这是不利于实际使用的,手动降频只能降到2.4,没法精确定位到2.5G。

所以希望各位明白一点就是当龙芯圈使用它们的话术比如IPC攻击其他国产芯片的时候不要简单的顺着套路走相信他们就好,咱是图吧的见过多年I炮N炮A炮互喷知道这事,但是各位如果对于芯片不甚了解又在国产这个新的赛道不小心着了他们的道就是大大的不妙了。现在有一种观点就是对国产失去信心比没有国产更可怕,舆情战败与汉芯悲剧--2018年原文 BV1wG411b7ip,即使是陈进当年好歹也是做了点事的,所以以此看来龙芯圈目前的行为的恶劣程度可想而知。希望各位面对龙芯圈攻击其他国产芯片的话术不听不信不传,对国产保持信心就可以了。

谢谢朋友们!