【开源骚客】FPGA超详细入门视频教程—FPGA就业培训超值视频

知者不言,言者不知。

学习:现实操作<-->抽象理论(勾通)

现实操作,就是指quartus、modelsim里的操作,抽象理论就是指普通教科书上的内容,这些东西大多十分抽象,没有结合软件操作来讲,经常让人云里雾里,不能将书上的理论和现实的操作联系起来。

————————————————————

我学过verilog语言,但不系统,这个视频很基础,所以我只是学并记录一些自己不熟悉不知道的东西。

————P3————

输入端口只有wire型,无reg型

————P4————

时间单位/时间精度(类比直尺的1cm、1mm)

Ctrl+A:全选

Ctrl + G:智能分组

————P5————

1.条件运算符的嵌套:

assign data_c = (sel_a==0) ? ( (sel_b==0)?data_a:0 ) : ( (sel_b==1)?data_b:0 )

2.always @(sel_a or sel_b or data_a or data_b) begin …… end

注意敏感信号列表

3.tb文件最好要把测试信号的所有情况考虑在内

————P6————

restart。

c语言常识:if…else…配对遵循就近原则。如果删改if…else…语句,可能会对原代码含义造成极大破坏。

——加上begin…end…可以保持各语句的独立性,推荐使用。——

pi:port in;po:port out

o:八进制;h:十六进制

————P7————

时延语句一般不可综合,也就是无法在非仿真文件里使用。

sys_rst_n:system_reset_negedge

不指定位宽:默认位宽为32bit

————P8————

产生源源不断的时钟:always #5 clk = ~clk;

localparam本地参数,这种常量表示应该大写。

quit -sim:退出当前的仿真

f没有值或为不确定态x:因为d、e先前没有值或者为不确定态x

阻塞赋值:语句的赋值立即执行,无延时

非阻塞赋值:语句赋值的执行有延时,最快也是当前时刻结束前的最后一刻。

这种赋值方式要注意一下。

非阻塞赋值是为了带时钟沿always块里寄存器的并行赋值,适合于时序逻辑,因为时序逻辑电路拥有存储电路。

————P9————

流水灯(跑马灯)

- 移位式:assign led <= {led[2:0], led[3]};

- 选择式:case语句;if…else…语句

把这部分管脚分配代码复制到新的文件中。

————P10————

“流水灯”升级,基于FPGA的呼吸灯设计 (dengkanwen.com)

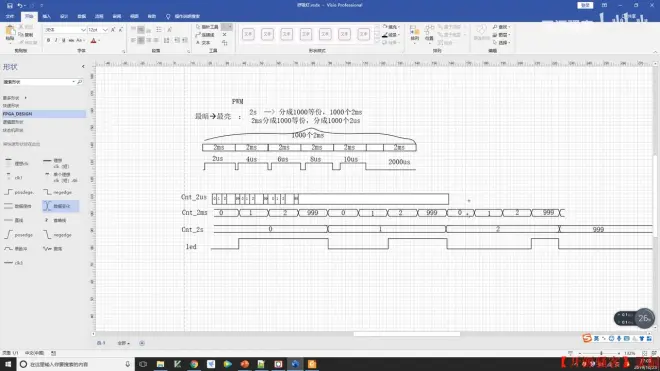

呼吸灯——使用PWM(Pulse Width Modulation脉冲宽度调制)波实现

2s

频率50Mhz<->周期20ns

2us的0-99指的是时钟的0-99。

2s分成1000个2ms,这1000个2ms中Led亮的时间依次递增

————P11————

画波形图十分重要,有助于代码直观化。

写if…else…语句时,要善于区别大条件和小条件。

————P12————

用flag_2s和&&逻辑与,实现分情况讨论

————P13————

按键消抖的讲解。抖动时间一般小于10ms

按键+抖动-->>高电平

————P14————

友情提示:跨时钟域处理可参考知乎文章,必应搜索即可

关键:在仿真时产生按键输入信号

————P15————

TOP-DOWN设计思想:分模块设计——简洁、易于开发

使用visio画图直观化设计。

————P16————

- analysis分析:对语法错误进行检查。

- synthesis综合:将verilog代码综合映射成FPGA资源内部的逻辑门,生成网表文件。

- 前仿真/功能仿真functional simulation:不考虑布局布线

- fitter电路适配器(place&route):布局布线

- classic timing analyzer经典时序分析器

- 后仿真timing simulation/TimeQuest Timing Analysis静态时序分析:考虑布局布线

- 上板验证/板级调试