1224 Class AB输出的浮动电流源偏置问题

实验室组会上提到了这个class AB输出结构,很有意思,是竞赛的题目。这篇论文非常经典,也被Sansen收录在他的圣经著作中,这种偏置结构他称之为translinear loop。

今天就来读一读这篇论文《A compact power-efficient 3 V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries》,并结合Ivanov的理解谈一谈这个结构。

class AB的浮动电流源结构是很常用的,相信大家也在各种书里见过,非常神奇,它为输出级n管和p管提供偏置,同时提供VG之间的一个电压差值,使两管同步导通,一起上拉下推。这里面其实还有不少变化和细节问题。两个浮动电流源的作用是不同的,论文中详细阐明了两者的区别,尤其左边,它不是必须的,而是一步步演变过来。

一、M16&M20——以共模反馈的观点看静态电流IQ的控制

Ivanov认为这种Class AB输出的行为与具有共模反馈的差分结构是一致的,沿用了一般的具有共模反馈的信号流图来表示这里的环路控制。

他是这么描述的,对于输出管MN和MP来说,有两个量需要控制,一个是输出电压Vout=(IN-IP)*ZL,还有一个是静态电流IQ。IQ经常通过其他自变量产生,必须创建同时控制两个晶体管的控制系统。在这种情况下,必须使用电流sensor——FP和FN来测量电流Ip和In,并将这两个电流的平均值与Iq进行比较,然后将其用于反馈控制回路。有以下两种流图描述这种行为:

a图中,这个环路应该有一个负增益-G的放大器(我们这里假设是电流放大器)。 该放大器的输出应该使用分配器或分路器进行分路,通过链路E1和E2向门节点变量IGP和IGN提供两个信号。 输入信号VIN应该通过跨导放大器A1和A2到达相同的节点。 如果栅极节点变量为电流,则对栅极节点电阻R1和R2进行求和,得到栅极驱动电压变量VGSP和VGSN。

b图是a图的一个等效图,是比较实用的。

以浮动电流源类型的Class AB输出级为例,可以这么理解:

该电路中的Class AB推挽操作由两个反馈环控制。 晶体管MNS为MN提供本地反馈回路,当MN的电流减小时增加电流IMNS(图7-3C的FN和gmns),起到保持MN栅极电压的作用,同时使晶体管MP导通(MNS的源极和漏极实现分配器功能操作)。这里IP和IN的电流sensor就是VGSP和VGSN,与VP、VN相减,则偏置电压VP、VN就是控制共模量IQ的关键所在。图中有一些量没有标出来,我在下图中重新标注了一下,作流图时应把RP、RN看作树,MPs和MNs看作余树。

关于这个浮动电流源对于第一级增益的影响,如果两管gm相同,那么相当于一个简单的1/gm电阻,可以忽略不计。如果gm不同,可以通过上面的流图计算出两端分别的增益(这里不展开了)。

二、M27&M28——叠加电流的巧妙方法

左边的这个浮动电流源更有来头了。我们一步步解释它的由来。

论文中说,最初的设计如图6,第一级就完完全全是个折叠cascode单级运放,然后搭上了后面的Class AB输出级,就是把上面的结构拼在一起。问题在于Ib6和Ib7两个电流源不但降低了增益,还引入了额外的噪声和失调,作者希望不要引入Ib7和Ib7这两个额外的电流源,于是变成了图8:

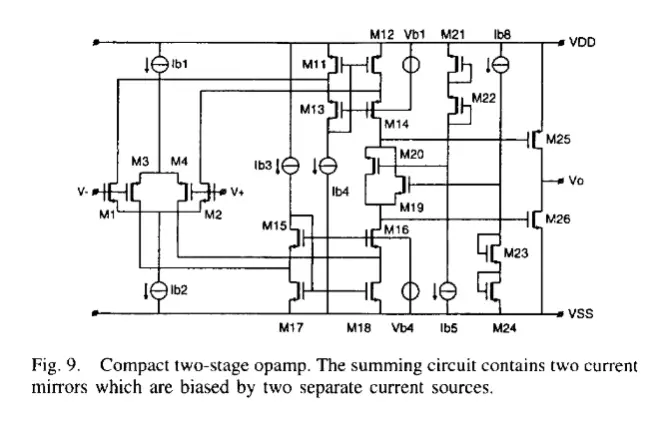

此电路有些问题,在于IQ受到共模输入电平的影响较大。由于Ib3、Ib4是限定死的,那么M20和M19的电流之和就等于Ib4减去输入P管的电流,变化较大。于是作者又想办法,不能将这里的Ib4限定死,希望底下的电流能随P管过来的电流变动而变动,而M16的电流保持不变。他分别做了两个电流源,通过折叠的电流源结构,实现了这一功能,得到图9:

但他还是对这个电路有些不满意,将Ib3和Ib4也合并掉了,得到图10:

除了节省掉一路电流,它还有额外的好处:Ib3产生的噪声由电流镜传过来叠加之后,两个相关的噪声抵消掉了!这不同于图9,图9中两路电流源是独立的非相关的,叠加到输出端时,噪声的方差要相加。

电流源Ib3应该采用何种结构呢,这是个浮空的电流镜,容易想到的是sansen书上的这种结构:

但作者不满足于这种固定电流的电流镜,而是使用了和电流叠加端相同的结构,如图11:

这种结构的一个缺陷是电流源的输出阻抗不够大,只有1/gm,所以会随输入共模电平的变化而有一定的波动。但这个波动不如图8那么直接,相当于有个电阻分流在这,变化会减小几倍。

好在如果设置的电流本身就够大(这样cascode管的gm大,还正好可以用上cascode补偿),那么输入级电流的变化再经过分流过来,影响就很小了。论文里输入级的电流是2.5uA,M19M20的电流是28uA。最后共模输入电平对Ifloat的影响大概只有5%。

那么为什么采用这种输出阻抗小的电流源呢?作者有他的理由,他希望电源对两边的影响是一致的,这样对静态电流IQ的影响最小。推导比较复杂,暂时也没有想到直观理解的方法。

扫描VDD,查看输出级N管的VGS,绿色采用了理想电流源,红色采用了文献中的电流源。可以看到,VDD的影响确实小了很多。

其实本身采用理想电流源,这个VGS变化也不是非常大。如果电路上下完全对称,那VDD的影响就是0。但N管和P管很难做到完全一样。

所以说这里有个取舍,要看共模电平和VDD哪个对IQ的影响更大以决定这里浮动电流源的结构选择。

总结

这个小小的电路蕴含着很多细节,左右两边结构一样,但作用却完全不同。Ivanov从共模反馈的角度来理解这里IQ的控制,非常深刻,很有意思。原论文中,考虑了很多影响IQ的因素,也考虑了噪声和失调的优化。在优化VCM的影响还是优化VDD的影响之间,选择了后者。