王道计算机考研 计算机组成原理

退伍考研 是因为心中还有梦

没有战胜不了的困难 倒计时196天

1.2_2_各个硬件的工作原理 P5 - 21:23

计算机各硬件的工作原理

- PC程序计数器(取地址)将指令写入地址寄存器MAR中

- 通过MAR所提供的地址,从存储体中取出对应的指令存入MDR数据寄存器中

- MDR有一条直接连通cpu的数据线,将数据发往IR指令寄存器中

- IR分析指令,将操作码发往CU控制单元,CU控制单元得出相应的操作

- IR将地址码,传到地址寄存器MAR,MAR取出地址码对应的数据,传入MDR中

- 由于CU发出的操作指令,将MDR中的数据传入运算器中的运算单元 ACC累加单元 MQ乘商单元等

- ALU算术逻辑单元 调配运算器中的运算工作,X 变址寄存器用于存放零时数据,例如上一次执行得出的数据,通过将上一次执行的数据放入X中,可将X中的数据再次作为运算的对象,实现多重运算的功能。

- 主存储器具有存取数据的能力,当CU收到存数的指令后,将运算器中的数据写入MDR,通过IR给出的地址码MAR读出其中的地址,将MDR中的数据存在相应的存储单元中。

PC程序计数器在取出程序后,地址自动加1

计算机系统的层次结构

- 汇编语言提供一种符号化的语言,需要通过汇编程序(编译器)翻译成机器语言

- 高级语言需要通过编译程序翻译成汇编语言,在从汇编语言编译成机器语言,但如今的一些高级语言,可以将高级语言直接编译成机器语言。

- 编译程序和解释程序的区别在于,编译程序是一次性将全部语句编译成机器语言,而解释程序是将源程序的一条语句进行翻译。 在规模足够大的时候解释程序来回执行编译,影响程序执行的性能。

计算机性能指标

- MAR的位数反映的存储单元的个数2的n次方

- MDR的位数反映的就是每个存储单元的大小

- 总容量就是二者相乘

1.3_计算机的性能指标 P7 - 07:39

- CPU的时钟周期就是一个脉冲的时间

- CPU的主频和时钟周期

- CPI指执行一条指令所需要的时钟周期,执行指令的时钟周期受到多方面因素的干扰,故讨论一条程序的耗时=CPI*CPU时钟周期.

1.3_计算机的性能指标 P7 - 14:42

- 其中关于单位容易弄混的点

- 在存储中K G T 表示的是2的十次方等等

- 在计算的性能指标中K表示10的三次方等等

1.3_计算机的性能指标 P7 - 18:33

此块内容影响的因素比较广泛

- 数据带宽,类比于车道,一次性能传输多少的数据

- 吞吐量 指一次性能消化和产出多少数据

- 响应时间 概念较为广泛 可以理解为数据的反应时间。

第二章 数据的表示和运算

- 八进制三位一组 十六进制四位一组

- r进制转十进制 各位上的权值相加

- 十进制转r进制 整数部分除基取余 小数部分乘基取整

2.1_2_BCD码 P9 - 11:34

- 8421码表示10-15要加上0110

- 2421码从5之后首位都是1

- 余3码在8421码基础上加0011

- 余3码是无权码

无符号整数运算

无符号减法 被减数不变,减数按位取反末位加一 然后两项相加

无符号整数加法直接按位相加

原码补码反码转换和加减法

- 原码首字符是符号位 表示的区间范围-2n次方-1到2n次方-1

- 正数的原码补码反码相同

- 负数的反码是原码除符号位外按位取反,补码是在反码的基础上1

- 带符号整数的加减法都要先转换成补码

- 带符号整数加法:补码按位相加符号位参与计算

- 带符号整数减法:被减数不变,减数的全部位按位取反,再加一,最后再按位相加

各种码的基本特性总结

可以通过手算带入十进制判断是否溢出

移码是在补码的基础上符号位取反

2.1_6_移码 P13 - 00:19

定点小数和定点整数的扩展位置不同

电路的基本原理和加法器的设计

ALU算术逻辑单元

- 与 全一为一 a*b

- 或 有一为一 a+b

- 非 取反

- 与非 有零为一 全一为零

- 或非 有一为零 全零为一

- 异或 相同为零 想异为一

- 同或 相同为一 想异为0

一位全加器

全加器设计原理

全家器有两个输入端 A1 B1

一个本位的和就是当前位置的数 S1

还有一个进位就是向前一位进的数Ci-1

不难理解本位只有奇数个1时才会为1所以通过异或将三个参数连接 A1(+)B1(+)Ci-1

而进位要为一必须11相碰 所以 AB和Ci-1 至少要两个为1 表达式如上图

并行加法器

n个全加器通过一个进位器并行起来 就可以形成n个位的加法

效率取决于进位的速度

加法器原理

- 加法器一共五个参数(被加数,加数,Cin低位的进位,Cout最高位的进位)

- 依托这五个参数设计各种加法器电路

补码的加法器设计原理

- 补码的加法器设计

- 添加一个多路选择器

- 多路选择器的0表示加法运算,1表示减法运算

- 多路选择器还释放出一个sub信号,将多路选择器当前的信号传递至Cin低位的进位

- 当多路选择器是信号0时,则直接进入加法器运算,当多路选择器是信号1时,则通过非电路按位取反后进入加法器,并且Cin接收到sub的1信号,低位进位加1

标志位的生成

标志位主要是记住标志位的硬件计算方法即可

定点数的移位运算

- 原码整数的算术移位操作

- 左移,后面补0前面溢出的舍去

- 右移,前面补0后面溢出的舍去

- 小数的计算也是同理,按照每一位的权值相加即可

- 反码的算术移位 正数和原码相同 负数左移低位补1 右移高位补1

- 算术补码的位移操作 正数不变 负数的左移补0 右移补1

- 移位的操作可以运用在计算机的乘法中

原码的乘法运算在机器中的实现

- 构想一个运算器的结构

- X存储被乘数 ACC存储乘积的高位 MQ存储乘积的低位 和乘数

- 第一步符号位单独处理 两个乘数之间的符号位用异或运算

- 初始化将ACC中的数据置0

- MQ中的最低位若为1 则 X 和 ACC 进行加法 若MQ中的最低位为0 则 ACC+0

- 当进行一次乘法操作后 在下一次乘法的开始时 将ACC右移一位 ACC的最低位 变成MQ的最高位

- 重复N次

补码的乘法实现的过程

补码的乘法运算结构包括

- 在MQ中引入了一个辅助位(初始值为0)因此MQ的长度为n+2

- 由于MQ中引入了一个辅助位,因为为了保持寄存器的一致 ACC和X中也引入辅助位 采取双符号表示因此长度也为N+2

- 补码的乘法运算是带符号运算

- 判定ACC加什么 :

- 如果辅助位-MQ最低位为1 ACC+X补

- 辅助位-MQ最低位为-1 ACC+[-X]补

- 辅助位-MQ最低位为0 ACC+0

5.加完一次之后算术右移 正数补0 负数补1

6.最后再来一次加法 但不右移

原码的除法

恢复余数法

- 首先出发的核心思想就是先进行一次减法 然后逻辑左移后面补零

- 恢复余数法 默认先商1(+【-y】) 发现ACC的值小于零 就+y恢复成原式即可

3.符号位的选取 x异或y的符号位

- 注意小数点的隐含位置

- 余数=得到的余数再*2 -n次方

4.左移的次数比商的次数少一次左移n次 商n+1次

1.加减交替法就是当商1 余数出现负时 直接左移一位 + 除数 得到下一轮的余数。

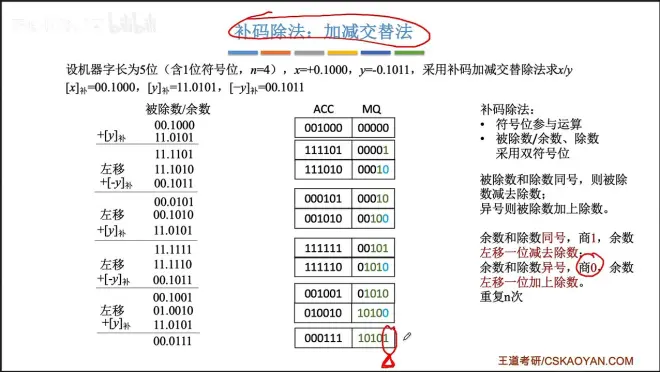

补码的除法运算

- 原码的符号位不参与运算,但补码的符号位参与运算

- 采用双符号位的形式

- 初始的被除数与除数的符号为异的则加上除数,同的则减去除数

- 余数和除数为同号则 左移 后减除数 异好则左移 后 加上除数

- 最后一位的商直接就变成1 误差不超过 2-n次方

- 最后的余数同样*2-n次方