ZYNQ使用AXI-Lite协议实现PS与PL简单通信

AXI-Lite是AXI(Advanced eXtensible Interface)总线协议的一个简化版本,主要用于连接低复杂性、低带宽要求的外设和处理器之间的通信。与完整的AXI协议相比,AXI-Lite协议具有更少的信号和简化的操作流程。

本文测试板子为正点原子领航者ZYNQ 7020,通过对Xilinx内部自定义AXI-lite IP核进行简单修改,实现PL读取PS端的DDR数据,对数据进行处理后再写入PS端的DDR,然后PS端在SDK内读取PL端写入DDR的数据。本文仅当一个简单测试记录

首先点击Tools创建一个AXI-Lite IP核

选择创建一个AXI4类型的IP核

IP核存放位置可以去掉../,存放在当前文件夹内

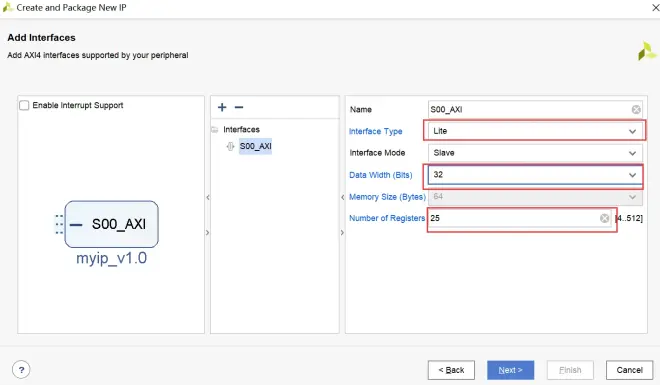

接口类型Lite,位宽只能选择32Bits,Number of Registers是选择定义多少个寄存器来从存储PS与PL通信的数据,一个寄存器可以存储32Bits,这里我选择25个数据,其中24个寄存PS向PL发送的数据,1个寄存PL向PS发送的数据。

上一步点击next后,选择Edit IP再点击Finish开始对该自定义IP核进行编辑

Vivado自动弹出IP核编辑窗口,这里一共两个文件,上面的是顶层例化文件,下面是实现PS与PL通信的文件,主要在下面文件进行修改。

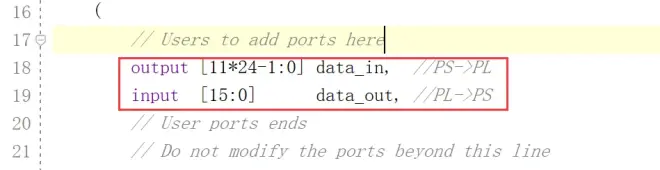

打开第二个文件,在Users to add ports here这里添加接口,第一个data_in是接收PS发过来的24个11Bits数据,我这里把11位数据的最高位作为数据有效信号(后面SDK的C语言代码可以看出),当然也可以单独发送一个data_valid,第二个data_out是PL向PS发送的一个16位数据。

接下来实在最后面添加自定义的逻辑,这里把24个PS发送到PL的32Bits数据的前11位拼接起来赋值给data_in,然后把PL端要发送到PS端的一个16位数据拼接成32Bits。

接着把读写状态代码的冗余部分进行注释,因为前0~23个寄存器是用来读的,所以把第24个写寄存器注释掉

这里读状态机对第24个寄存器读也要注释掉

注释完冗余的读状态内的写寄存器,再把写状态内的读寄存器注释掉,只保留第24个寄存器是PL向PS写数据。

最后在顶层添加接口

保存后,一次点击下面完成IP核的封装,再打包IP核

创建一个Block Design,添加ZYNQ IP与上面自定义的AXI-Lite IP核,打开ZYNQ的UART通信接口(具体操作可以看正点原子领航则SDK指导教程)再配置好DDR类型

在自动弹出的Address Editor内可以更改寄存器的起始地址,这里使用默认起始地址

整体Block Design,这里的top_bpnet是我写的一个bp网络,可以接收PS端发送的24个11Bits的温度数据进行预测,预测的结果是一个16位的数据再发回到PS端,这里可以用自己写的数据处理模块。

为了查看AXI-Lite协议的传输方式,可以对一些信号debug,选中三个数据线,右键debug

进行自动debug连线后保存设计,把block design设为顶层最后生成bitstream

打开SDK,创建一个main.c文件,代码也很简单,主要通过调用Xil_In32与Xil_Out32两个函数实现对DDR内存的读写。

打开串口调试,随便发送1~24,串口返回一个预测数值

转到Vivado界面,写入bitstream文件及debug文件,先查看PL从PS第去24个32Bits数据,ILA触发条件为WVALID与WREADY同时为高,即两个信号成功握手

在SDK内使用串口发送0~24进行触发,可以看见AXI-Lite在WVALID与WREADY握手后,向地址0x04(注意这里的地址要加上基地址才是真正的地址)写入1040,这里是1040是因为我把1*16+1024,这里加上1024是相当于把第11位置1充当有效信号。第二数据是向0x08写入1056,对应SDK里的2*16+1024

再把触发条件换成RREADY与RVALID握手

可以看到PL端向0x64地址写入的数据是361,这里是0x64转成十进制是100,因为每个数据是4Byte即32Bits,PL向PS写数据是保存在第25个寄存器,映射在DDR的地址是25*4=100,

这里的写入DDR的数据361除以16就是串口打印的22.562