RK3588 PCB Layout通用布线规范,附《RK3588 PCB设计指导白皮书》

注意:布线之前须把软件默认设置选项设置好,并打开DRC检测开关。布线建议打开5mil格点,等长时可根据情况设置1mil格点。(文末附《RK3588 PCB设计指导白皮书》下载入口)

1.1 关于PCB线宽

1、布线首先应满足工厂加工能力,首先向客户确认生产厂家,确认其生产能力,如图4-1所示。如客户无要求,线宽参考阻抗设计模板。

图4-1 PCB板厂线宽要求

2、阻抗模板,根据客户提供的板厚及层数要求,选择合适阻抗模型,布线线宽按阻抗模型内计算的宽度进行设置,常见阻抗为单端50Ω,差分90Ω、100Ω等,注意天线50R信号是否应该考虑隔层参考。

图4-2 常见的PCB层叠

3、如图4-3所示,布线线宽需要满足载流能力。一般情况下,可以基于经验、考虑布线余量,可以按照:温升在10°C,对于铜厚1OZ,20MIL线宽过载电流1A;铜厚0.5OZ,40MIL线宽过载电流1A来进行电源线宽设计。

图4-3 PCB线宽载流表

4、常规设计线宽应尽量控制在4MIL以上,此线宽能满足大部分PCB生产厂家加工能力。对于部分不需要控制阻抗的设计(大部分为2层板设计),保证线宽在8mil以上,减少PCB的生产加工成本。

5、布线应考虑所在层铜厚设置,如2OZ尽量设计在6mil以上,铜厚越厚,线宽越宽,对不常见铜厚设计,可咨询生产厂家的加工要求。

6、0.5mm、0.65mm间距BGA设计可在部分区域使用3.5mil线宽设计(可设计区域规则管控)。

7、HDI板设计可选择3mil线宽设计,低于3mil设计必须向客户确认加工工厂的生产能力,部分厂家生产能力为2mil。线宽越细,加工成本增加,加工周期延长。

8、模拟信号(如音视频信号)须加粗处理,一般处理为15mil线宽,如空间限制,应控制在8mil以上线宽。

9、射频信号应加粗处理,隔层参考,阻抗控制50。射频信号应处理在表层,避免处理到内层,尽量避免打孔换层处理。射频信号须包地处理,参考层尽量参考GND铜皮。

1.2 关于PCB布线线距

1、布线首先应满足工厂加工能力,线距应满足工厂生产能力,一般控制在4mil以上;0.5mm、0.65mm间距BGA设计可在部分区域使用3.5mil线距设计,HDI可选择3mil线距设计,低于3mil设计必须向客户确认加工工厂的生产能力,部分厂家生产能力为2mil(可设计区域规则管控)。

2、线距规则设计之前须考虑设计的铜厚要求,1OZ尽量保持4mil以上距离,2OZ尽量保持6mil以上距离。

3、差分信号对内距离应按阻抗要求进行设置距离。

4、布线应远离板框位置,尽量保持板框位置能包地打GND孔,保持信号离板边40mil以上距离。

5、电源层信号比GND层内缩10mil以上距离。电源与电源铜皮宽度应保持10mil以上距离,部分IC(如BGA)因间距较小,可适当调整其距离,设置到6mil以上(可设计区域规则管控)。

6、重要信号,如时钟、差分、模拟信号等,须满足3W距离或者包地处理。线与线之间的距离保持3倍线宽。是为了减少线间串扰,应保证线间距足够大,如果线中心距不少于3倍线宽时,则可保持70%的线间电场不互相干扰,称为3W规则,如图4-5所示。

图4-5 3W原则

7、相邻层信号避免平行布线,走线方向成正交结构,以减少不必要的层间窜扰,如图4-6所示。

图4-6 垂直与平行走线

8、布线在表层时,应远离定位孔,距离保持在1mm以上,以防安装时出现短路或者安装应力产生的线路撕裂导致开路,如图4-7所示。

图4-7 螺丝孔的避空区域

9、电源层平面分割应注意一个电源平面不要分割的太碎,一个电源平面内处理的电源尽量不要超过5个电源信号,最好控制在3个电源信号以内,以保证载流能力及规避相邻层信号跨分割风险,如图4-8所示。

图4-8 电源平面的分割

10、电源平面分割要尽量保持规则,不允许有细长条及哑铃形分割,避免出现两头大中间小的情况,并根据电源铜皮最窄处宽度计算其载流能,如图4-9所示。

图4-9 电源平面的哑铃形分割

1.3 关于PCB布线方式

1、走线长度应包含过孔和封装焊盘的长度。

2、布线角度优选135°角出线方式,任意角度出线会导致制版出现工艺问题。

图4-10 PCB布线的角度

3、布线避免直角或者锐角布线,导致转角位置线宽变化,阻抗变化,造成信号反射,如图4-11所示。

图4-11 走线的锐角与直角布线

4、布线应从焊盘的长方向出线,避免从宽方向或者焊盘四角出线,布线的拐角离焊盘位置6mil以上为宜,如图4-12所示。

图4-12 PCB沿焊盘长边出线

5、如图4-13所示,相邻焊盘是同网络的,不能直接相连,需要先连接出焊盘之后再进行连接,直接连接容易在手工焊接时连锡。

图4-13 相同网络焊盘走线链接方式

6、对于小CHIP器件,要注意布线的对称性,保持2端布线线宽一致,如一个管脚铺铜,另一管脚也尽量铺铜处理,减少元件贴片后器件漂移旋转,如图4-14所示。

图4-14 CHIP类焊盘的正确出线

7、对于有包地要求的信号,须保证包地的完整性,尽量保证在包地线上进行打GND孔处理,2个GND孔间距不能过远,尽量保持在50-150mil左右,如图4-15所示。

图4-15 PCB的包地走线

8、走线应有完整且连续的参考层平面,避免高速信号跨区,建议高速信号距离参考平面的边沿至少有 40mil,如图4-16所示。

图4-16 走线的夸分割

9、由于表贴器件焊盘会导致阻抗降低,为减小阻抗突变的影响,建议在表贴焊盘的正下方按焊盘大小挖去一层参考层。常用的表贴器件有:电容、ESD、共模抑制电感、连接器等等,如图4-17所示。

图4-18 布线的环路面积的缩小

10、如图4-18所示,信号线与其回路构成的环路面积要尽可能小。环路面积小,对外辐射小,接收外界的干扰也小。

图4-17 标贴器件焊盘的挖空处理

11、如图4-19,布线不允许出现STUB,布线尽量减小残桩长度,建议残桩长度为零。并且避免过孔残桩效应,尤其是残桩长度超过 12mil 时,建议通过仿真来评估过孔残桩对信号完整性的影响,如图4-20所示。

图4-19 Stub走线及布线残桩

图4-20 过孔的残桩

12、尽量避免走线在不同层形成自环。在多层板设计中容易出现此类问题,自环将引起辐射干扰。如图4-21所示。

图4-21 PCB布线的自环

13、建议不要在高速信号上放置测试点。

14、对于会产生干扰或者敏感的信号(如射频信号),须规划屏蔽罩,屏蔽罩宽度常规为40mil(一般保持30mil以上,可与客户生产厂家确认),屏蔽罩上尽量多打GND过孔,增加其焊接效果。如图4-22所示。

图4-22 敏感模块的屏蔽罩处理

15、同一网络的布线宽度应保持一致,线宽的变化会造成线路特性阻抗的不均匀,当传输的速度较高时会产生反射。在某些条件下,如接插件引出线,BGA封装的引出线类似的结构时,因间距过小可能无法避免线宽的变化,应该尽量减少中间不一致部分的有效长度,如图4-23所示。

图4-23 走线线宽的突变

16、IC管脚出线的线宽要小于或者等于焊盘宽度,出线宽度不能比焊盘宽度大,部分信号因载流等要求,线宽较宽的,布线可先保持与管脚宽度一致,布线引出焊盘后6-10mil左右再把线宽加粗处理,如图4-24所示。

图4-24 走线不宜超出焊盘宽度

17、布线必须连接到焊盘、过孔中心。

18、有高压信号,须保证其爬电间距,具体参数如4-25所示。

图4-25 爬电间距与电气间隙表

19、设计中包含多片DDR或者其他存储器芯片的,须向客户确认布线拓扑结构,确认是否有参考文档。

20、金手指区域需要开整窗处理,多层板设计时,金手指下方所有层的铜应作挖空处理,挖空铜皮的距离板框一般3mm以上,如图4-26所示。

图4-26 金手指的开窗与挖空

21、布线应提前规划好瓶颈位置的通道情况,合理规划好通道最窄处的布线能力。

图4-27 PCB布线通道

22、耦合电容尽量靠近连接器放置。

23、串接电阻应靠近发送端器件放置,端接电阻靠近末端放置,如eMMC时钟信号上的串接电阻,推荐放在靠近 CPU 侧(400mil以内)。

24、建议在IC(如eMMC 颗粒、FLASH颗粒等)的地焊盘各打1个地通孔,有效缩短回流路径, 如图4-28所示。

图4-28 GND焊盘的过孔打孔

25、建议ESD器件的每个地焊盘都打一个地通孔,且通孔要尽量靠近焊盘,如图4-29所示。

图4-29 ESD器件GND焊盘的打孔

26、避免在时钟器件(如晶体、晶振、时钟发生器、时钟分发器)、开关电源、磁类器件、插件 过孔等周边布线。

27、走线换层,且换层前后参考层为地平面时,需要在信号过孔旁边放一个伴随过孔,以保证回流路径的连续性。对于差分信号,信号过孔、回流过孔均应对称放置,如图4-30(a)所示;对于单端信号,建议在信号过孔旁边放置一个回流过孔以降低过孔之间的串扰,如图4-30(b)所示。

图4-30(a)差分换层过孔示意图

图4-30(b)单端信号换层过孔示意图

28、连接器的地铜皮距离信号 PAD至少要大等于3倍线宽,如图4-31所示。

图4-31 GND铜皮与连接器PAD的间距要求

29、在BGA区域平面断开处用走线连接,或者进行削盘处理,以免破坏平面完整性,如图4-32所示。

图4-32 BGA区域平面铜皮的处理

30、PCB布线需要包地处理时,推荐包地方式如下,如图4-33所示,L 为包地线地过孔间隔;D 为包地线距离信号线之间的间距,建议≥4*W。

图4-33 PCB的包地布线

31、有些重要的高速单端信号,比如时钟信号、复位信号等(如emmc_clk、emmc_datastrobe、RGMII_-CLK 等等)建议包地。包地线每隔 500mil 至少要打一个地孔,如图4-34所示。

图4-34 重要信号线的包地处理

1.4 关于PCB过孔扇出

1、过孔的主要作用是用于信号的换层连接,设计中使用过孔必须要在不同层连接信号,不能只连接一层,导致其产生STUB。散热过孔除外。

2、同一设计中选用的过孔数量不宜过多,一般不多于3种。常规过孔大小为8/16、10/22、12/24,特殊情况下可选用8/14、10/20、10/18类型过孔,HDI设计一般选用4/10、4/8类型激光孔。一般优先选择过孔孔径大的类型,可提高生产的合格率,减少生产成本。2层板原则上选择12/24类型过孔设计。

3、过孔选择须考虑板厚、孔径比,对于板厚较厚的设计,须选用大的过孔类型。有特殊铜厚设计要求的,优先选用孔径大的过孔,如条件不允许,及时与板厂沟通其生产能力要求。

4、选择过孔类型及设计数量应考虑其载流能力。为保证设计余量,有空间会按计算的2倍数量处理,如图4-35所示,可以基于设计具体要求进行选择。

图4-35 PCB设计过孔的选择

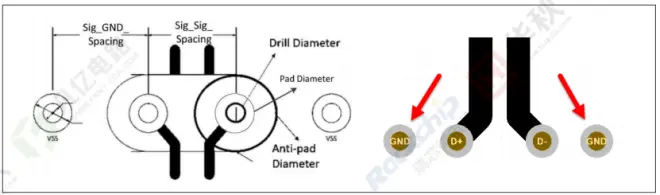

5、过孔扇出要考虑其间距,要求2个过孔之间保证能过一根信号线,防止过孔破坏地与电源的完整性。2个过孔之间的中心间距建议在1mm以上(39.37mil),如图4-36所示。

图4-36 过孔打孔要求

6、IC扇出优先选择外侧,有多排尽量调整地与电源的信号过孔扇出到管脚附近。左右2边过孔应保持在同一水平线上,以方便内层布线。如图4-37所示。

图4-37 过孔的扇出要求

7、如图4-38所示,电容扇出应保证其到供电管脚环路最小。过孔避免打到盘上,以免造成焊接不良,增加生产成本。一定要打盘中孔应将孔打在管脚边缘,不能打到中心位置。

图4-38 电阻容的过孔扇出原则

8、板边须沿着板框内缩的位置,打一圈GND过孔,过孔与过孔的距离在50-200mil左右,如图4-39所示。

图4-39 屏蔽GND孔

9、BGA器件扇出时,过孔应打在2个焊盘对角线中心,并向四周扇出,中间十字通道禁示打过孔,保证其电源通道的载流能力,如图4-40所示。

图4-40 BGA的扇出十字通道

10、BGA器件扇出时可考虑将前面2排孔拉出去一段距离,拉出去的过孔要与BGA中间的过孔尽量保持对齐,以方便BGA器件信号的内层出线,如图4-41所示。

图4-41 BGA走线技巧

11、一般可根据BGA器件间距,估算每层出线的数量,规划出所需设计板层。一般1mm间距以上的,一个通道可以布2根信号线,1mm间距以下一个通道过1根信号。0.4mm间距一般只能进行HDI设计。

图4-42 不同BGA过孔之间出线数量

12、器件大于0805封装的,建议采用十字连接处理。大面积铺铜的通孔焊盘一般采用十字连接处理,特别是对于多层板的GND网络通孔管脚,防止焊接时散热过快导致焊接不良。

图4-43 焊盘的铺铜链接方式

13、多层板设计时,避免大面积无铜情况产生,以防某一区域内在多层都无铜存在,板子上各处密度差异过大,温度变化时热胀冷缩导致板子出现弯曲,特别是面积比较大的。

14、PCB设计完成后,须对板子上的铜皮进行修铜处理,将铜皮尖角消除,须检查PCB上的孤铜,严禁孤铜的存在。

图4-44 孤铜的移除

15、差分信号换层时,其换层过孔附近必须添加GND过孔,保证其回流路径短。

图4-45 打孔换层时添加GND孔

16、差分信号2个过孔中间,所有层保持净空,禁示其他信号通过,如图4-46所示。

图4-46 差分过孔中间禁止布线

17、差分信号出线方式应保持耦合与对称,尽可能的减少不耦合长度,如图4-47所示。

图4-47 差分线的对于与耦合

18、BGA器件扇出时为了方便滤波电容摆放,可将电源和地孔进行合孔处理,一般允许2个管脚合用1个过孔,不允许多个管脚共用1个过孔。设计时应尽量避免合孔处理,以保障电源和地的载流能力。

图4-48 BGA 焊盘的合孔处理

19、建议在高速连接器的每个地焊盘至少打一个地通孔,并且通孔要尽量靠近焊盘,如图4-49所示。

图4-49 连接器的GND焊盘

1.5 关于PCB走线等长要求

1、在做 PCB 设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的 PCB 信号等长处理。等长的目标是为了满足同组信号的时序匹配要求。

2、等长范围应严格遵守不同接口或者信号的要求,具体的可参考模块规范内容。如若有疑问,及时与客户进行确认。

3、处理等长之前应先把同组内线长最长的信号线找到,第一步优化最长信号的长度。

4、等长处理完后应对整根信号线路径进行检查,检查其是否避开干扰源,检查其是否合格。

5、等长处理时,间距优选4W,如空间受限,可调整到3W;等长高度控制在40-150mil为宜,不能过高;转角长度不小于线宽的1.5倍,一般控制在6-10mil大小,如线宽4mil,转角大小控制在6mil,转角不能太小,如图4-50所示。

图4-50 蛇形走线的要求

6、等长应尽量处理在水平或竖直方向上,避免处理在斜线上;处理不能太过散乱,应尽量集中处理,保证其美观性,原则上是处理完一根信号后,第二根先修线挨到其旁边,再对第二根进行等长处理,以保证空间的利用率及整体设计美观性。同一设计内,等长的高度应控制差不多相同,不要相差太多,如图4-51。

图4-51 PCB的蛇形咬合等长

7、处理完等长后,应检查其参考层情况,不允许其跨分割。PCB上时钟信号(一般以clk结尾)等重要信号也要避免跨分割情况出现,跨分割后会导致信号阻抗突变。

图4-52 PCB布线夸分割

8、当走线的参考平面有跨电源层时,建议在2个电源层分别加对地电容以提供完整的回流路径,如图4-53所示。

图4-53 走线夸分割处理

9、差分信号对内等长位置应在不耦合产生的位置附近进行等长,对内等长高度及宽度参考下图4-54示要求。

图4-54 差分线的等长要求

1.6 RK3588 BGA的扇出设计

1、最外面两圈的Ball扇出设计

靠最外圈Ball,可以从TOP层走4mil线宽出去;第二圈的信号从两个 Ball中间走4mil线宽走线出去,建议设置栅格,从两个Ball正中间走线出去,如图4-55所示。

图4-55 RK3588 扇出示意图1

2、内圈的Ball扇出设计

如果第一,二圈信号都有使用,那么第三圈开始,需要换层到内层,务必换层过孔规则放置,并且建议间隔2-4排换层过孔,空一排不放置换层过孔,给地平面以及电源平面留出尽量大的通道。如下图地层平面覆铜情况,有多条通道和外面的地连接,有利于SI/PI以及散热,如图4-56所示。

图4-56 RK3588扇出示意图 2

如下图4-57所示,电源层平面覆铜情况,有规则的放置过孔,可使各种电源有尽量大覆铜通道,有效提高电源供电质量。

图 4-57 RK3588扇出示意图3

如下图Bottom层走线(内层走线类似),换层过孔按栅格设置,放在Ball正中间,可在两个过孔之间走3.5mil 线宽扇出,如图4-58所示。

图4-58 RK3588 扇出示意图4

—————————————————————————