数电学习笔记26——常用的组合逻辑电路(2)

教材:阎石《数字电子技术基础》(第五版) 高等教育出版社

视频教材:

4.3.2 译码器

(1) 功能:将每个输入的二进制代码译成对应的输出高、低电平信号或另一个代码。

(2) 译码是编码的反操作。

一、二进制译码器

(1) 功能:输入一组二进制代码,输出一组与输入代码对应的高、低电平。

(2) 3位二进制译码器的框图、真值表如图。

(3) 采用二极管与门阵列构成的3位译码器

① 二极管与门阵列构成的3位译码器电路如图。

② 二极管与门阵列译码器工作原理、真值表如图。

③ 二极管与门阵列的译码器优点:电路简单;缺点:输入电阻低、输出电阻高,输出的电平信号发送偏移。

④ 二极管与门阵列的译码器通常只在一些大规模集成电路内部采用,中规模集成电路译码器多采用三极管集成门电路。

(4) TTL与非门构成的74LS138

① 74LS138译码器的逻辑图、逻辑函数如图。

② 在门电路的图形符号中,有时为了强调“低电平有效”,会在输入端处加上小圆圈,同时在信号名称上加非号。

③ S1=1、S’2+S’3=0时,译码器处于工作状态。否则译码器所有输出端被封锁在高电平。

④ 74LS138译码器的功能表如图。

(5) 用两片3线—8线译码器组成4线—16线译码器

(6) 用作多路分配器

设置使能端S1=1,S2和S3作为数据输入端,A0、A1、A2作为地址输入端,那么S2和S3送来的数据只能由A2A1A0所指定的一根数据线送出去。

四、用译码器设计组合逻辑电路

由于n位二进制译码器的输出给出了n变量的全部最小项,因而用n变量二进制译码器和或门或者与非门定能获得任何形式输入变量数不大于n的组合逻辑函数。

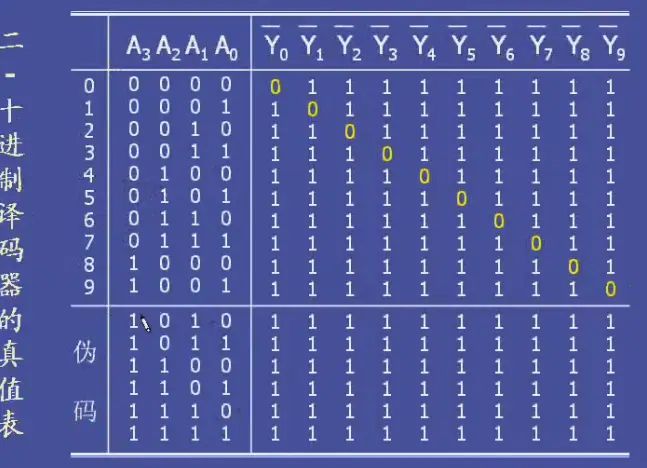

二、二—十进制译码器

(1) 功能:将输入BCD码的10个代码译成10个高、低电平输出信号。

(2) 二—十进制译码器74LS42的逻辑图、真值表如下:

(3) 对于BCD码以外的伪码,Y’0~Y’9均为低电平信号产生,所以这个电路有拒绝伪码的功能。