神电测控:LabVIEW FPGA番外篇:实验60:LVDT传感器测量位置和位移的原理与FPGA编程

1、概览

本篇KS详细介绍了LVDT传感器并解释了它们的工作原理;并且详细说明了测量 LVDT的要求以及测量所需的信号调理;最后,给出了一个国外LSET公司开发的9312 C模块,可以直接插到NI cRIO平台上采集LVDT传感器并自动完成校准解析。当然,后续我们也会单独给出如何利用通用的FPGA开发板和模块来完成对LVDT传感器的解析案例程序和驱动VI。

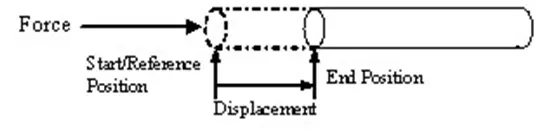

2、什么是线性位移测量

线性位移是指单个轴在一个方向上的运动。线性位置或位移传感器是一种设备,其输出信号表示物体从参考点移动的距离。位移测量还可指示运动方向,如图1所示。线性位移通常以毫米(mm)或英寸(in.)为单位以及与之相关的正反方向。

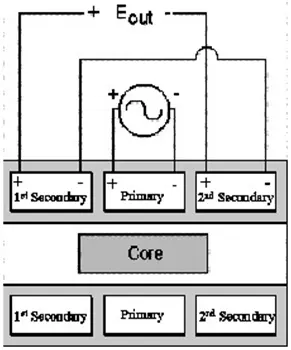

3、线性可变差动变压器 (LVDT)

线性可变差动变压器(LVDT)可以用于测量位移,因为LVDT的基本工作原理是变压器。如图2所示,LVDT由线圈组件和磁芯组成:线圈组件通常安装在固定组件上,而磁芯则固定在需要被测量位置的物体上。线圈组件由缠绕在空心组件上的三个线圈组成,可渗透材料的核心可以自由地滑过模板的中心。内部线圈是初级线圈,由交流电源激发,如图2所示。初级产生的磁通量耦合到两个次级线圈,在每个线圈中感应出交流电压。

与其他类型的位移传感器相比,LVDT传感器的主要优点是高度的坚固性。由于传感元件之间没有物理接触,传感元件就不会存在磨损。另外,由于设备依赖于磁通量的耦合,因此LVDT具有无限分辨率。因此,可以通过调节合适的信号来检测运动的最小部分,这样换能器的分辨率则完全由数据采集系统的分辨率决定。

4、LVDT测量

LVDT通过将特定信号值与磁芯的任何给定位置相关联来测量位移。信号值与位置的这种关联是通过初级绕组上的交流激励信号与磁芯和次级绕组的电磁耦合而发生的。磁芯的位置决定了初级线圈的信号耦合到每个次级线圈的紧密程度,两个次级线圈是串联相对的,即意味着串联但方向相反,这就导致了每个次级上的两个信号相位相差180度。因此,输出信号的相位决定了方向及其幅度和距离。

图3描绘了LVDT的横截面图。磁芯使初级绕组产生的磁场耦合到次级绕组,如图所示,当磁芯完美地位于次级和初级之间时,每个次级中感应的电压幅度相等,相位相差 180度。因此,LVDT 输出(对于本例中所示的串联相反连接)为零,因为电压相互抵消。

将磁芯向左移动会导致第一个次级与初级的耦合比第二个次级更强,如图4所示。第一次级相对于第二次级产生的较高电压导致与初级电压同相的输出电压。

同理,将磁芯向右移动会导致第二个次级与初级的耦合比第一个次级更强,第二次级的较大电压导致输出电压与初级电压异相,如图5所示。

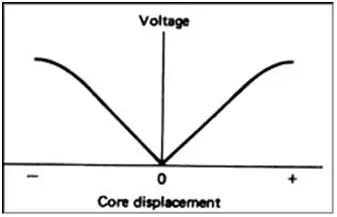

总而言之,LVDT模拟了理想的低频零阶位移传感器结构,其中输出是输入的直接线性函数。它是一种可变磁阻设备,其中初级中心线圈建立磁通量,该磁通量通过中心磁芯(可移动电枢)耦合到初级两侧对称缠绕的次级线圈。因此,通过测量电压幅值和相位,就可以确定磁芯运动的程度和方向,即位移。图6显示了器件在磁芯位移范围内的线性度。需要注意的是:当磁芯在其范围的边界附近移动时,输出不是线性的。这是因为从初级耦合到磁芯的磁通量较少。但是,由于LVDT具有出色的重复性,所以两头靠近边界的非线性还可以通过激光干涉仪进行校准和拟合的。

5、LVDT 的信号调理

因为LVDT的输出信号是交流波形,所以它没有极性。无论相对于零位移动的方向如何,LVDT的输出幅度都会增加。

为了知道磁芯的中心位于被测器件的哪半边,必须考虑输出的相位以及与初级绕组上的交流激励源相比的幅度(归一化)。输出相位与励磁相位进行比较,它可以与励磁源同相或异相,具体取决于磁芯中心位于线圈的哪一半。

信号调节电子设备必须将输出相位信息与输出幅度信息结合起来,这样用户才能知道磁芯移动的方向以及它移动到相对零位置的距离。

LVDT信号调节器会产生一个正弦信号作为初级线圈的激励源。该信号频率通常在50Hz到25kHz之间。一般情况下,我们选择的载波频率至少比磁芯(固定在被测对象上)运动的最高预期频率大10倍。信号调理电路会使用相同的初级激励源来同步解调次级输出信号。产生的直流电压与磁芯位移成正比,直流电压的极性表示位移是朝向还是远离第一次级(位移向左或向右)。

图7显示的是一种较为实用的检测方案,通常会集成到专为 LVDT 制造的单个集成电路 (IC)提供。该系统包含1个用于初级的信号发生器、1个相敏检测器(PSD)和放大器/滤波器电路。

LVDT传感器的测量范围还是很宽广的,线性范围从至少±50 cm到 ±1mm。时间响应取决于磁芯所连接的设备。LVDT测量的单位通常为mV/V/mm或mV/V/in。这表明,对于施加到LVDT的每一伏刺激,每单位距离都有一个明确的mV反馈。精密设计制造的LVDT可以在磁芯运动范围内提供±0.25%以内的线性输出,并具有非常精细的分辨率,当然,分辨率主要受限于信号调理硬件测量电压变化的能力。

6、如何连接LVDT

LVDT通常采用4 线(明线)和5线(比例线)配置。传感器的电线连接到信号调节电路,该电路将LVDT的输出转换为可测量的电压。图8和图9中的两个电路分别描述了与调节电路的4线制和5线制外部连接方式。注意:电线的颜色可能会有所不同。

4线和5线配置的区别在于来自第一和第二次级的信号的调节方式。在4线配置中,仅测量两个次级之间的电压差。以下等式将测得的电压与位移相关联,其中G是增益或灵敏度:

使用4线配置的好处是用户只需要外接一个简单的信号调理系统即可完成采集,但是坏处是,这是以初级激励电压和由此产生的次级电压之间的温度稳定性和相位相干性为代价的,温度变化会改变 LVDT的磁感应效率,这会导致给定位移的感知电压发生变化。另外,因为4线方案对初级电压和由此产生的次级电压之间的相位变化也很敏感,长导线或不良的激励源也会导致问题。

5线配置对初级和次级之间的温度变化和相位差不太敏感。温度稳定性的原因在于,由于磁感应效率的变化而导致的电压变化对电压V CH+和 V CH-的影响相对于地相等,因此消除了温度的影响。同样,相位信息由信号调节电路确定,无需参考主激励源的相位,因此,可以在LVDT和信号调节电路之间使用更长的导线。以下等式将测得的电压与位移相关联,其中G是增益或灵敏度:

8个模拟输入中的每一个都包含1个仪表放大器、1个可变增益级、1个解调电路和一个250 Hz低通滤波器。激励电压可设置为1或3 Vrms,频率为2.5、3.3、5或10kHz。

7、NI给出的成熟方案

NI的联盟商SET公司研发了一款名为9312的C模块,如图10所示,该模块可以插到cRIO机箱里面,直接测量外部的LVDT传感器并完成数据校准和解析,在后续的实验里面,我会给大家讲解如何使用通用的FPGA开发板和模块来实现对LVDT的激励、信号采集和数据解析。

https://www.smart-e-tech.de/portfolio-items/lvdt-9312-demodulator/

8、神电测控采用通用的黑金FPGA开发板和AD/DA模块实现LVDT仿真和采集计算(摆脱NI昂贵硬件限制,用户可以自由开发)